## Experiment No. 12 Successive Approximation A/D Converter ECE 446

Peter Chinetti

December 4, 2014

Instructor: Professor Shanechi

#### 1 Introduction

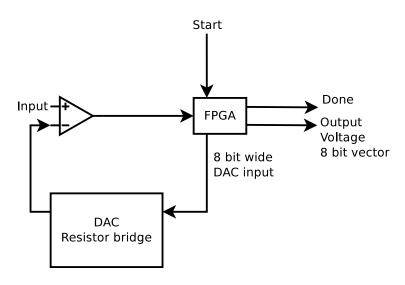

When working with real world signals, it is useful to be able to sample voltage levels. In this lab, the design of the Analog to Digital Converter is improved and implemented.

The translation is done with a DAC and a comparator. The sample voltage is held to one end of the comparator, and the DAC is tied into the other side. Each bit (starting with the MSB) in the DAC is set, the comparator output is tested, and unset if the signal goes too high.

This algorithm improves the two problems with the previous design. It takes time proportional to the logartithm of the number of output state, and it takes constant time to preform for all inputs. The only situation where this design performs more poorly than the original design is when the input voltage is lower than 4 DAC divisions.

# 2 Pre-Lab Questions

## 2.1

#### 2.3

Maximum error occurs when the input is very close to, but slightly less than, one of the DAC's output voltage. In that case, the voltage gets rounded down to the voltage below. This corresponds to (at the limit) an error of  $\frac{V_r}{2^n}$ . For a  $V_r = 5V$  and n = 4, the maximum error is 0.3125 volts.

## 3 Procedure

- a. Build resistor net and comparator circuit

- b. Write VHDL to implement ADC

- c. Assign pins to ports

- d. Simulate

e. Program and Test

## 4 Equipment

- PC

- Spartan-3E development board

- Op-Amp

- Assorted resistors and diodes

- Breadboard

#### 5 Code

#### 5.1 Top-Level Module

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity sar_fsm is

Port ( start : in STD_LOGIC;

en : in STD_LOGIC;

dac_out : out STD_LOGIC_VECTOR (3 downto 0);

result : out STDLOGIC_VECTOR (3 downto 0);

done_out : out STD_LOGIC;

clk_in : in STD_LOGIC);

end sar_fsm;

13

architecture Behavioral of sar_fsm is

type state is (DONE, COMP_B3, SET_B2, COMP_B2, SET_B1, COMP_B1,

SET_B0, COMP_B0);

signal p, f : state;

17

signal clk_i : STD_LOGIC;

component selectable_clock is

Port ( clk : in std_logic;

s0 : in std_logic;

s1 : in std_logic;

out_clk : out std_logic);

end component;

25

begin

div : selectable\_clock

27

port map(

clk \implies clk_in ,

s0 \implies '1',

s1 \Rightarrow '1',

31

out_clk \implies clk_i);

dac_out <= q;

```

```

result <= q;

35

process (clk_i)

37

begin

if rising_edge(clk_i) then

39

p \ll f;

q \ll d;

end if;

end process;

process (p, en, start, q)

45

begin

case p is

47

when DONE =>

if start = '0' then

49

d \ll q;

f \le DONE;

51

done_out <= '1';

53

else

f \le COMP.B3;

d <= "1000";

{\tt done\_out} <= \ '0';

57

end if;

when COMP_B3 =>

\begin{array}{l} f <= SET\_B2\,;\\ done\_out <= \ '0\,'; \end{array}

59

if en = '0' then

61

--d(3) <= '0';

d \leftarrow q and "0111";

63

else

\mathrm{d}\, <=\, \mathrm{q}\,;

end if:

when SET_B2 =>

67

f <= COMP_B2;

done_out <= '0';

69

-d(2) <= '1';

d <= q or "0100";

71

when COMP_B2 \Longrightarrow

f <= SET_B1;

done_out <= '0';

73

if en = '0' then

--d(2) <= '0';

d \ll q and "1011";

else

d \ll q;

79

end if;

when SET_B1 =>

81

f <= COMP\_B1;

{\tt done\_out} <= \ '0';

83

-d(1) \le '1';

d \le q \text{ or "0010"};

85

when COMP_B1 =>

f <= SET_B0;

done_out <= '0';

87

if en = '0' then

--d(1) <= '0';

d \le q \text{ and "} 1101";

91

```

```

else

\mathrm{d}\,<=\,\mathrm{q}\,;

end if;

when SET_B0 \Rightarrow

95

f <= COMP\_B0;

done_out <= '0';

97

-d(0) <= '1';

d <= q \text{ or "0001"};

99

when COMP_B0 =>

f <= DONE;

101

done_out <= '0';

if en = '0' then

--d(0) <= '0';

d \ll q and "1110";

else

d <= q\,;

107

end if;

end case;

109

end process;

end Behavioral;

```

$sar_fsm.vhd$

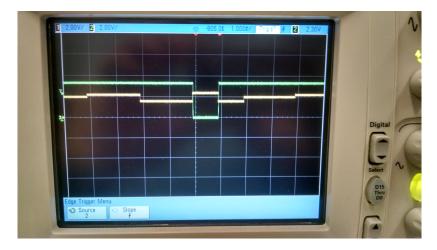

## 6 Scope Trace

## 7 Conclusions

The purpose of this lab was achieved. An improved ADC was built and tested. Operation was verified through simulation and physical implementation.