# PlanAhead User Guide

UG632 (v14.6) June 26, 2013

#### **Notice of Disclaimer**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: <a href="https://www.xilinx.com/warranty.htm#critapps">https://www.xilinx.com/warranty.htm#critapps</a>.

© Copyright 2009-2013 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. MATLAB and Simulink are registered trademarks of The MathWorks, Inc. All other trademarks are the property of their respective owners.

#### **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                                                                     |

|------------|---------|----------------------------------------------------------------------------------------------|

| 06/26/2013 | 14.6    | Added information on running ModelSim in Simulation Settings in Chapter 3.                   |

|            |         | Add information on IP Settings in Chapter 3.                                                 |

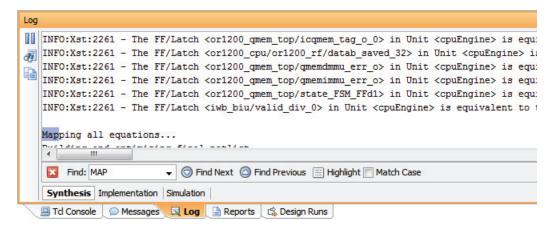

|            |         | Changed Compilation view to Using the Log view in Chapter 4.                                 |

|            |         | Removed Slack Histogram command from Chapter 7, Synthesized Design Constraints and Analysis. |

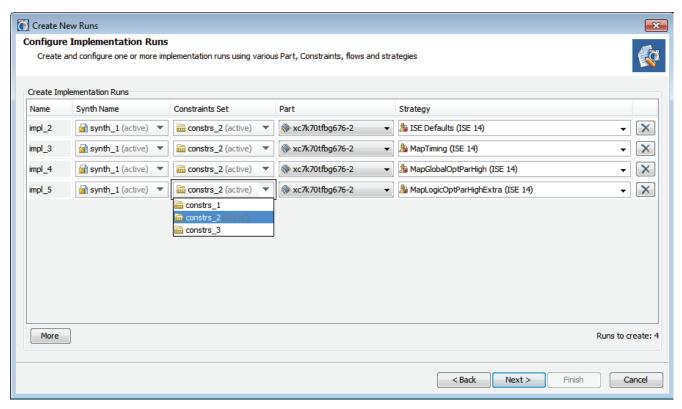

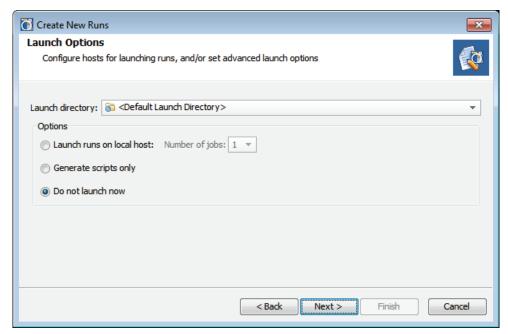

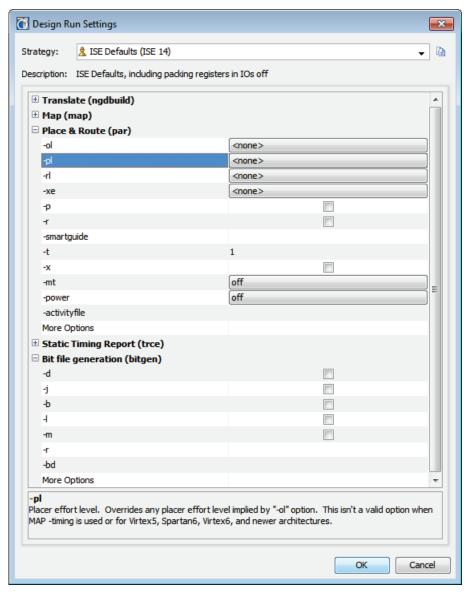

|            |         | Updated creating new implementation runs in Defining Implementation Runs in Chapter 9.       |

|            |         | Minor updates throughout.                                                                    |

|            |         |                                                                                              |

## Table of Contents

| Revision History                         | 2   |

|------------------------------------------|-----|

| Chapter 1: About the PlanAhead Tool      |     |

| About PlanAhead Software                 | 7   |

| Using the PlanAhead Tool                 |     |

| Launching the PlanAhead Tool             |     |

| Chapter 2: The PlanAhead Tool Flow       |     |

| Design Flow                              | 16  |

| User Models                              |     |

| Understanding the Flow Navigator         |     |

| Working with Designs                     |     |

| working with Designs                     | ,   |

| Chapter 3: Working with Projects         |     |

| Project Types                            |     |

| Creating a New Project                   | 37  |

| Managing Projects                        | 51  |

| Managing Project Sources                 | 52  |

| Managing Constraints                     | 53  |

| Managing Design Source Files             | 58  |

| Managing Simulation Sources              | 64  |

| Managing IP Cores                        | 66  |

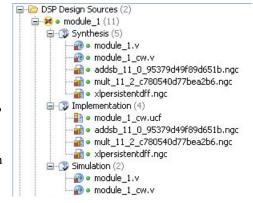

| Managing DSP Sources                     | 72  |

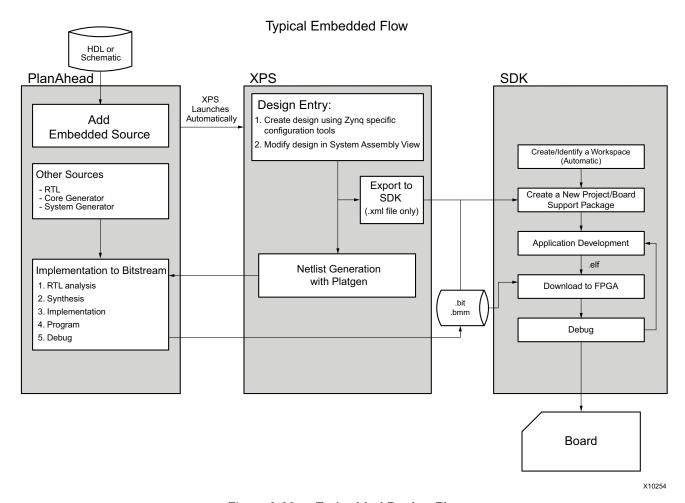

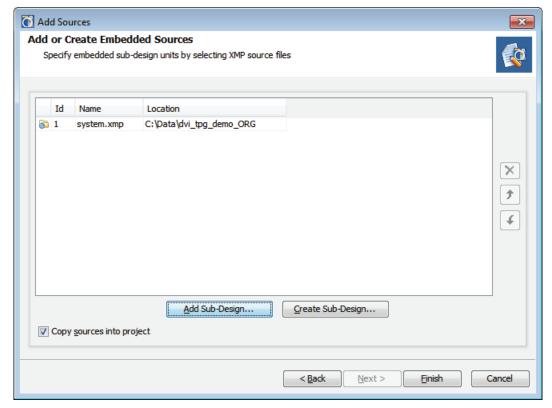

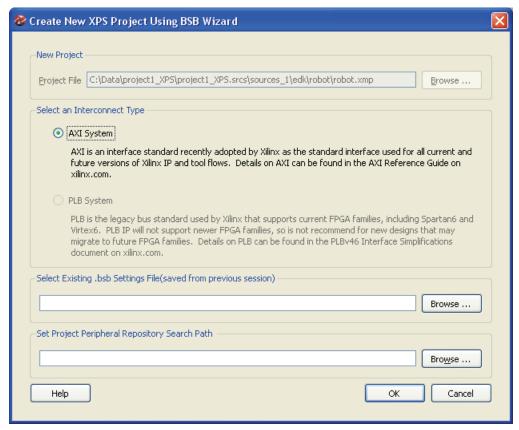

| Managing Embedded Processor Sources      | 75  |

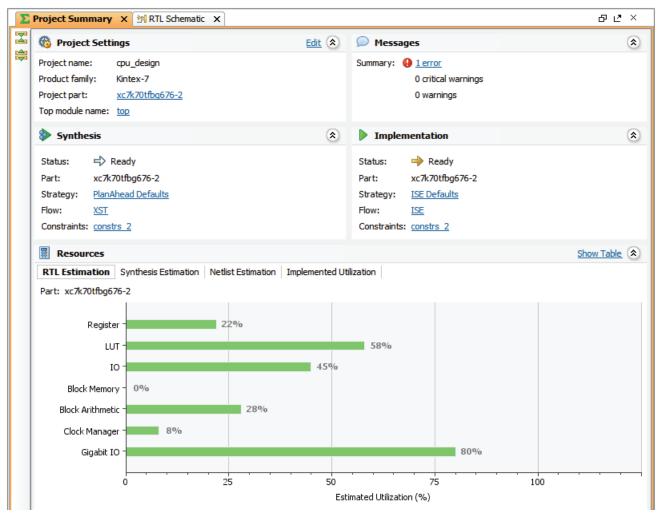

| Using the Project Summary view           | 84  |

| Configuring Project Settings             |     |

| Chapter 4: Using the Viewing Environment |     |

| The Viewing Environment                  | 97  |

| Using the Main Viewing Area              | 100 |

| Using the Tcl Console and Messages Area  |     |

| Working with Views                       |     |

| Selecting, Marking, and Moving Objects   |     |

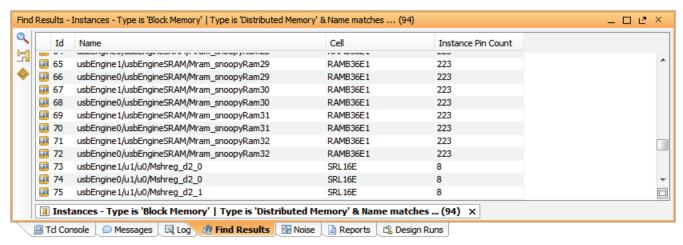

| Using the Find Commands                  |     |

| Using Common Views                       |     |

| Using the Text Editor                    |     |

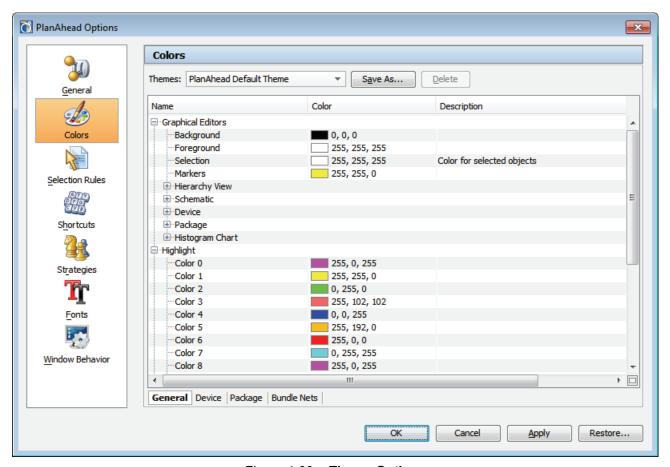

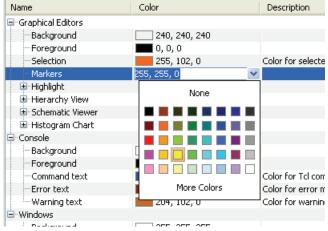

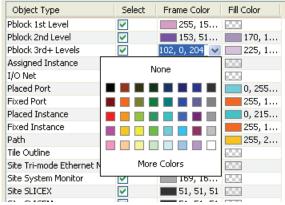

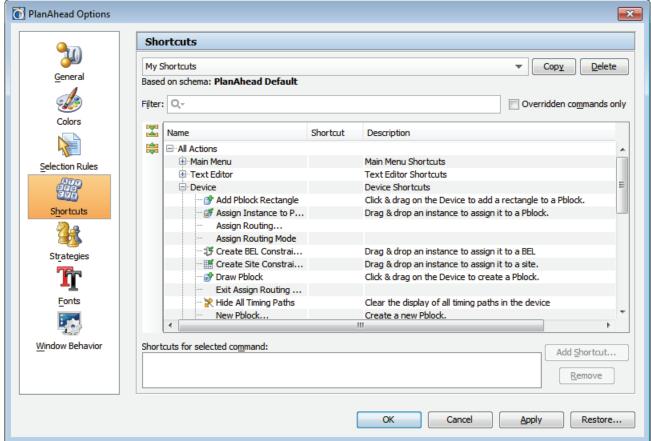

| Configuring PlanAhead                    |     |

| Chapter 5: Elaborated RTL Design                       |     |

|--------------------------------------------------------|-----|

| Managing Design Source Files                           | 183 |

| Editing RTL Source Files                               |     |

| Elaborating and Analyzing the RTL Source Files         | 184 |

| Performing Behavioral Simulation                       |     |

| Running RTL DRCs                                       |     |

| Chapter 6: Synthesizing the Design                     |     |

| Synthesis Methodology                                  | 197 |

| Running Synthesis                                      | 200 |

| Monitoring the Synthesis Run                           | 205 |

| Following Synthesis                                    | 206 |

| Analyzing Synthesis Results                            | 207 |

| Chapter 7: Synthesized Design Constraints and Analysis |     |

| Using the Synthesized Design Environment.              | 209 |

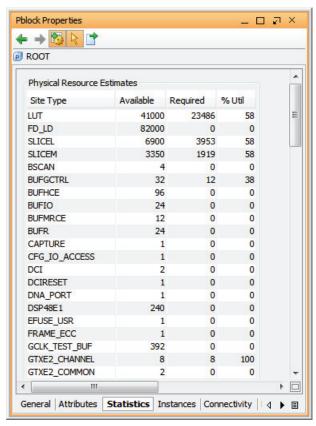

| Viewing and Reporting Resource Statistics              |     |

| Exploring the Logic                                    |     |

| Inserting ChipScope Debug Cores                        |     |

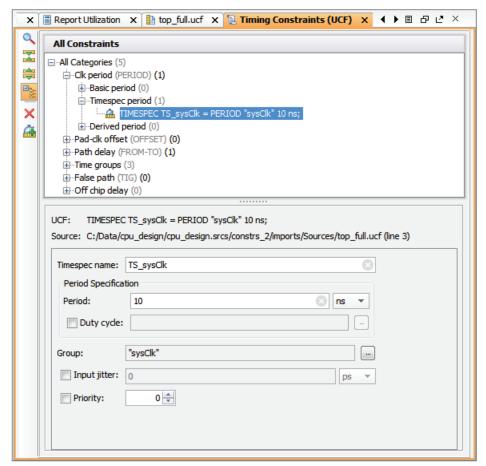

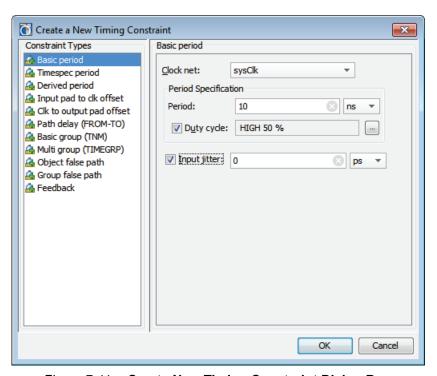

| Defining Timing Constraints                            | 219 |

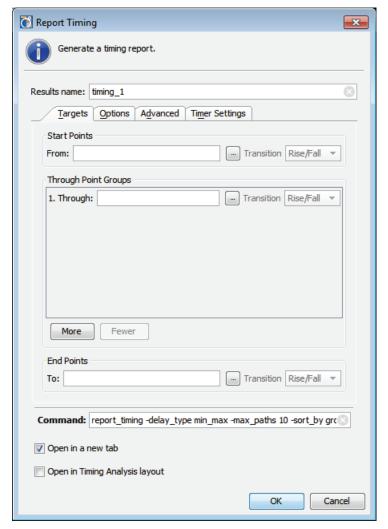

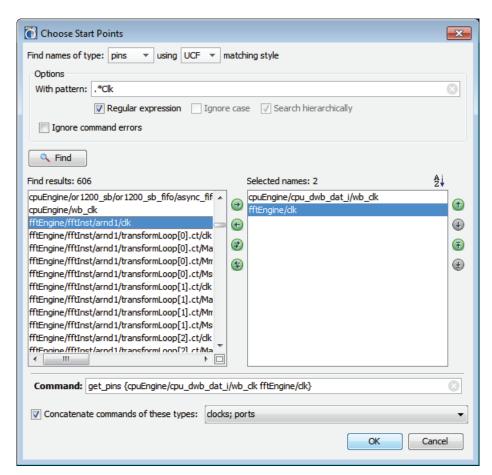

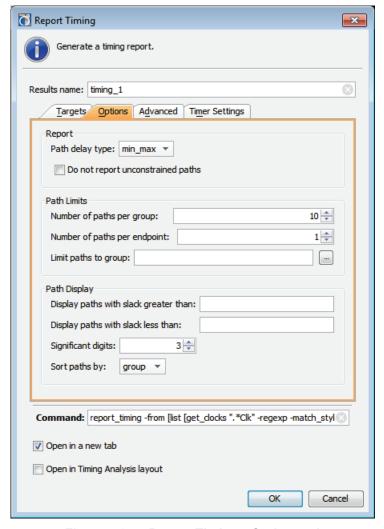

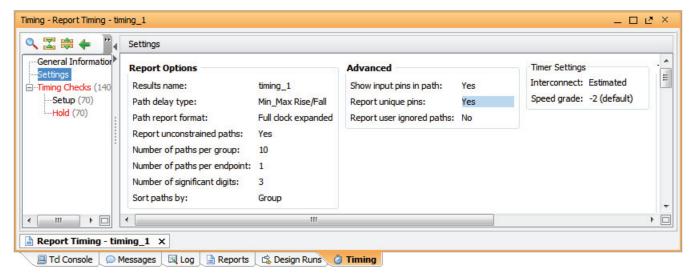

| Running Timing Analysis                                | 222 |

| Analyzing Clock Interactions                           | 233 |

| Defining Physical Constraints                          | 238 |

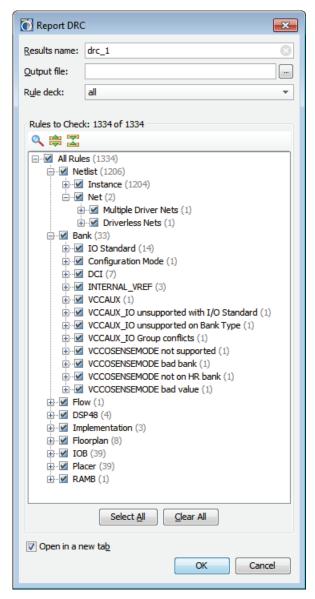

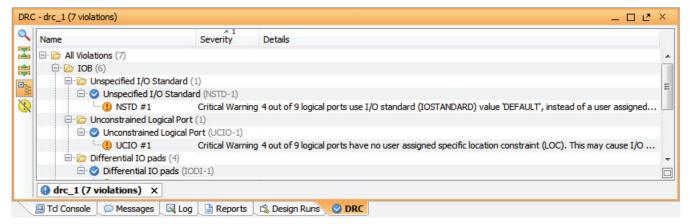

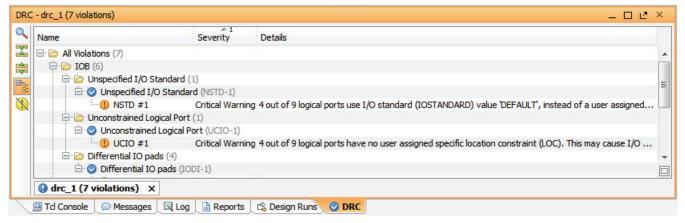

| Running the Design Rule Checker (DRC)                  | 242 |

| Chapter 8: I/O Pin Planning                            |     |

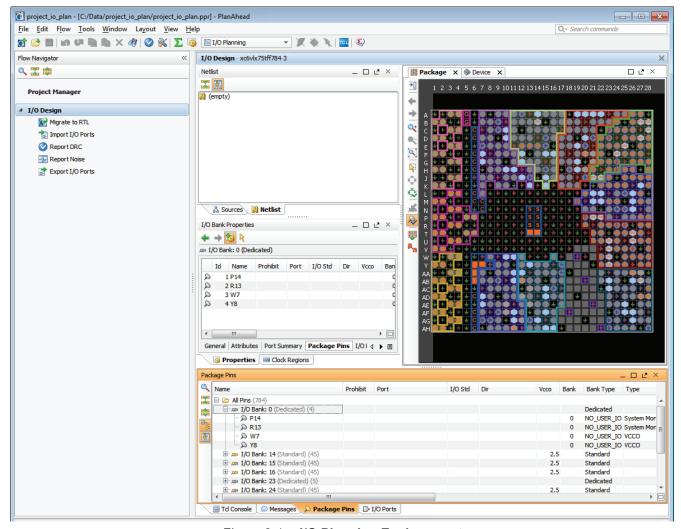

| I/O Pin Planning Methodology                           | 245 |

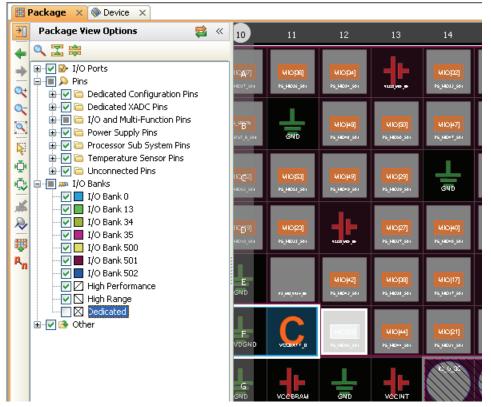

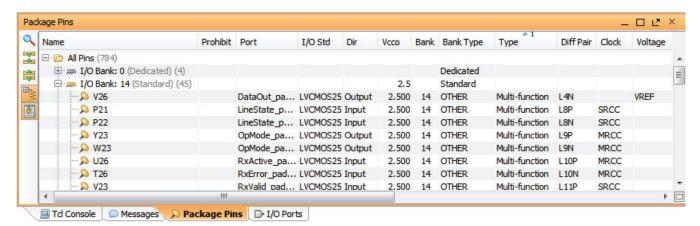

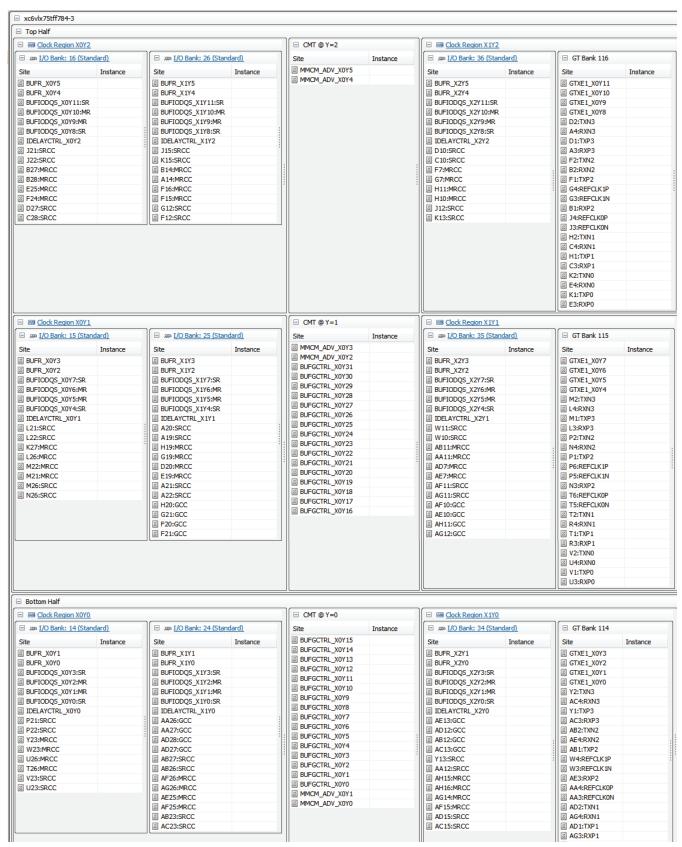

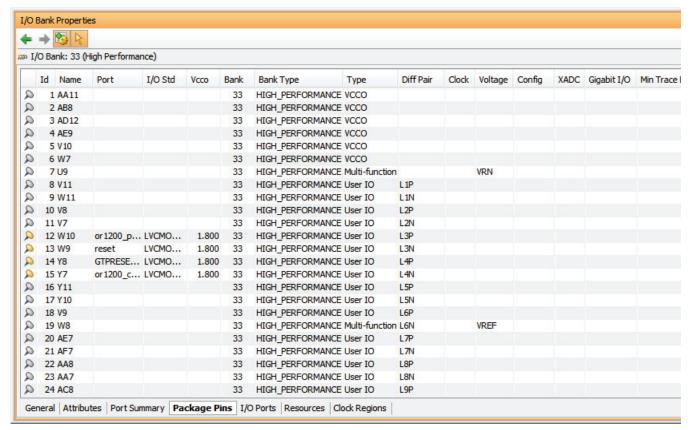

| Using the I/O Planning view layout                     | 247 |

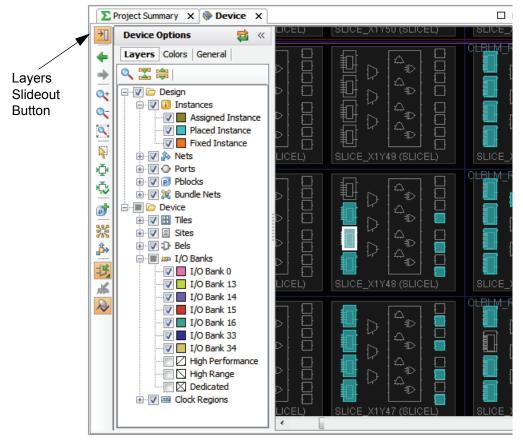

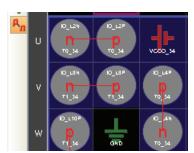

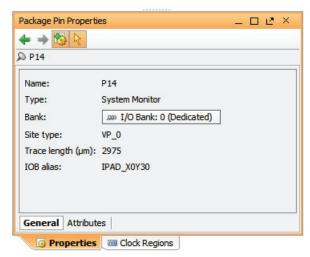

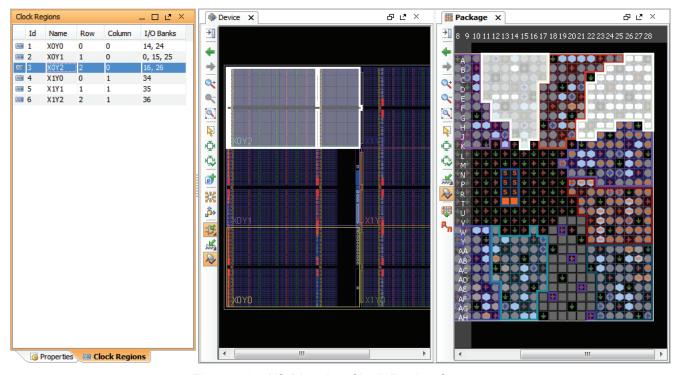

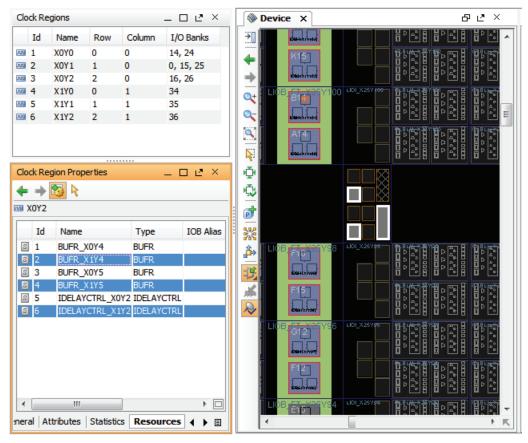

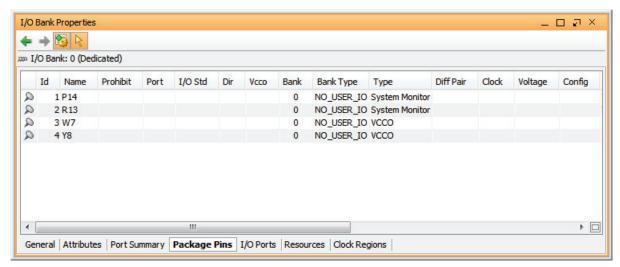

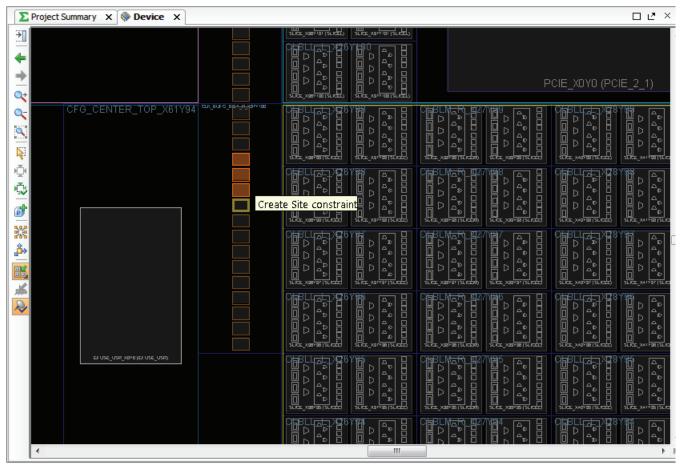

| Viewing Device Resources                               | 248 |

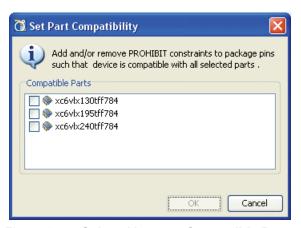

| Defining Alternate Compatible Parts                    | 252 |

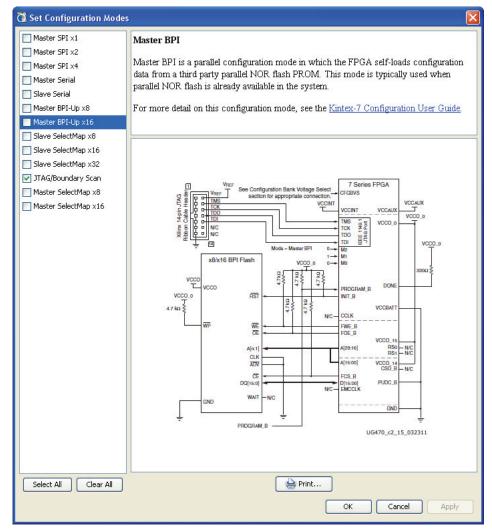

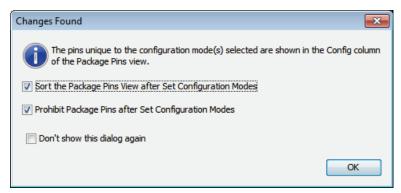

| Setting Device Configuration Modes                     | 253 |

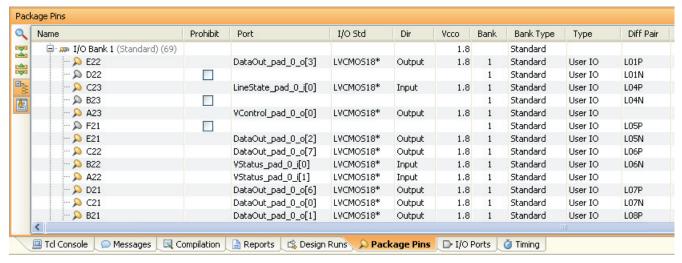

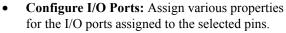

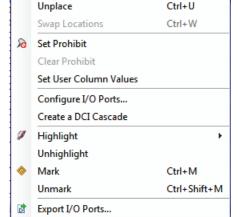

| Defining and Configuring I/O Ports                     | 254 |

| Disabling or Enabling Interactive Design Rule Checking | 262 |

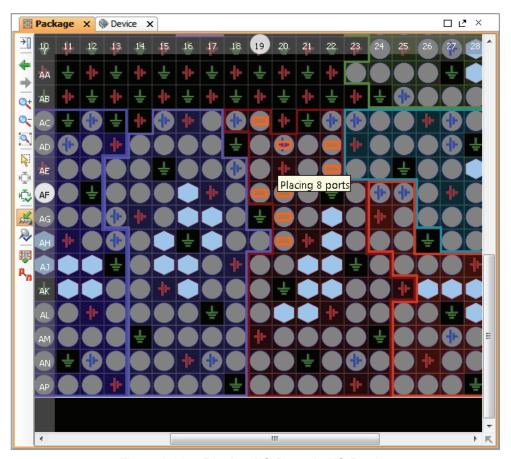

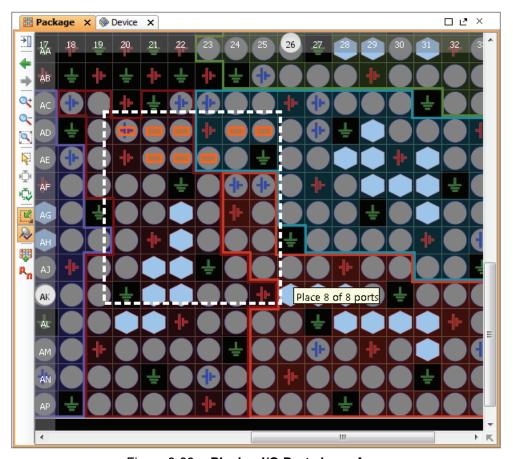

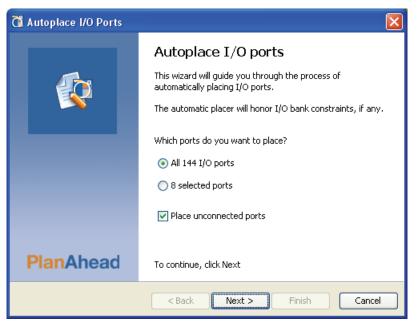

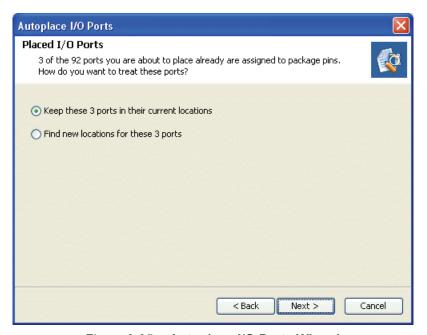

| Placing I/O Ports                                      | 263 |

| Placing Clock Logic                                    | 269 |

| Validating I/O and Clock Logic Placement               | 273 |

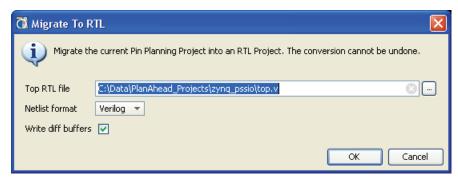

| Migrating to an RTL Design                             |     |

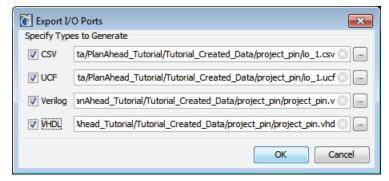

| Exporting I/O Pin and Package Data                     |     |

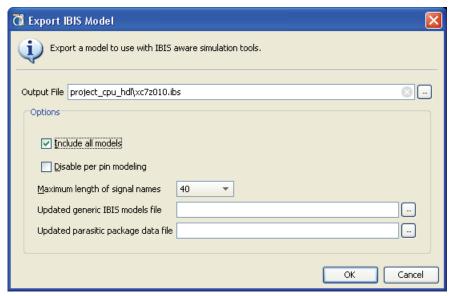

| Exporting IBIS Models                                  |     |

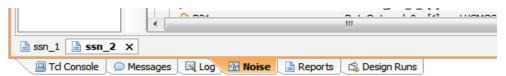

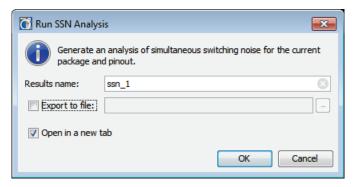

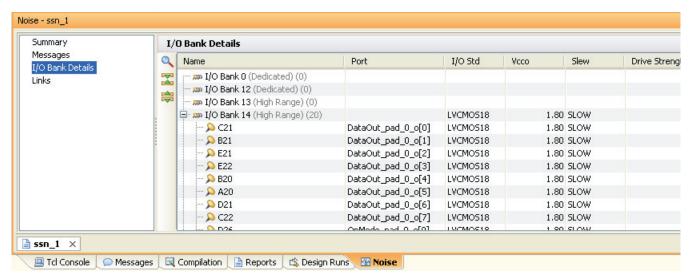

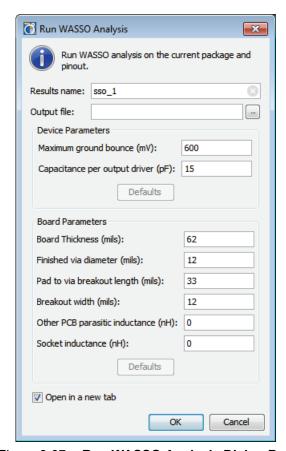

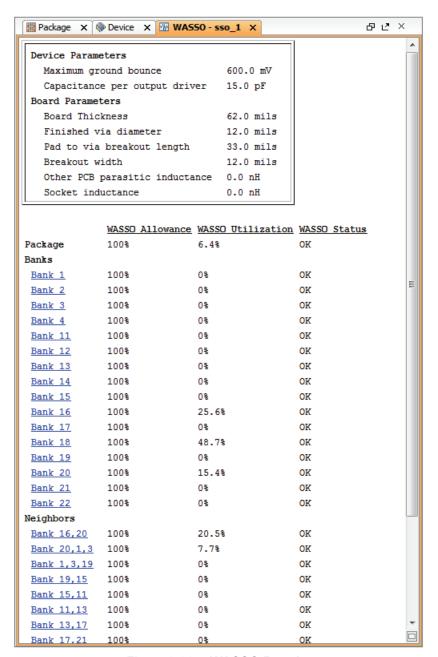

| Using Noise Analysis Predictors                        | 278 |

| Chapter 9: Implementing the Design                |     |

|---------------------------------------------------|-----|

| Running Implementation                            | 287 |

| Monitoring the Implementation Run                 | 294 |

| Determining the Project Status                    | 296 |

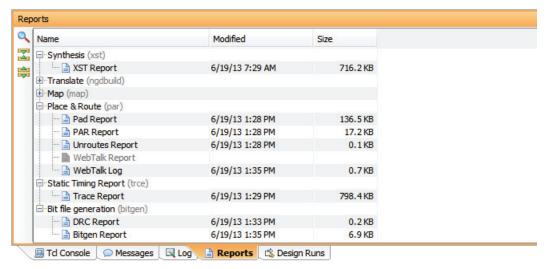

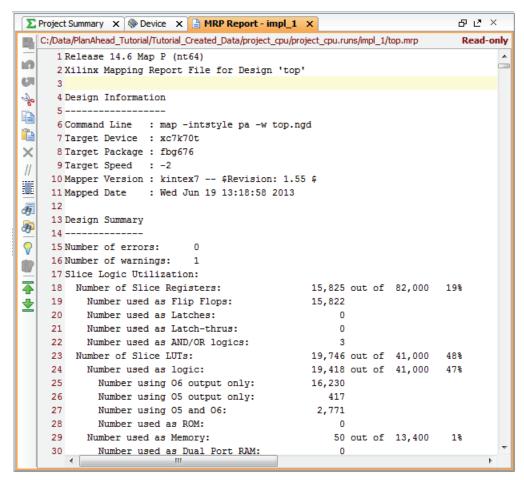

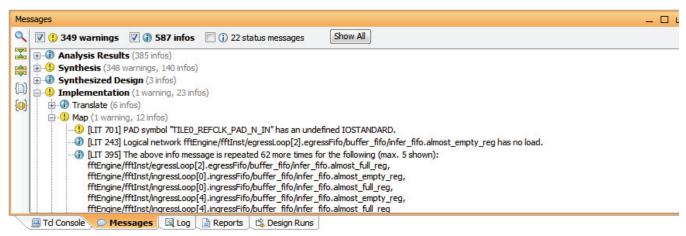

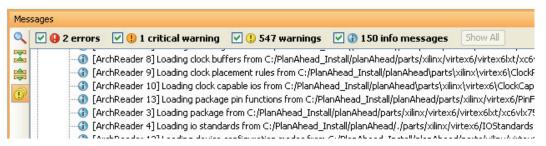

| Analyzing Implementation Run Results              | 297 |

| Following Implementation                          | 300 |

| Launching Runs on Remote Linux Hosts              | 300 |

| Chapter 10: Floorplanning the Design              |     |

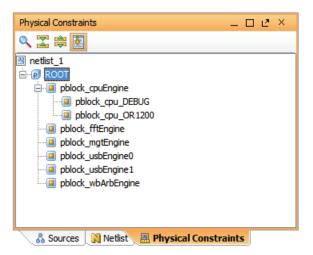

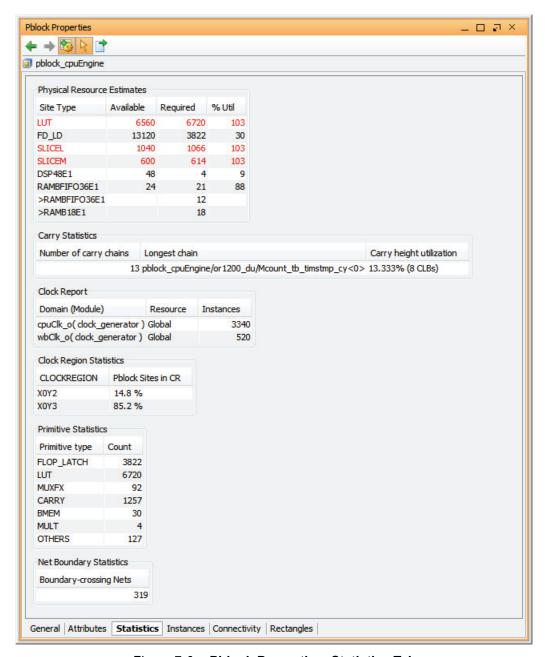

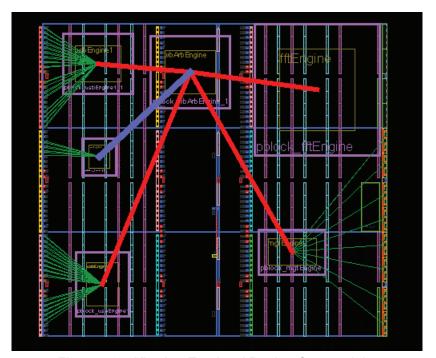

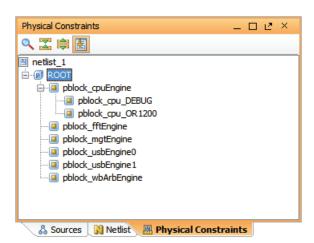

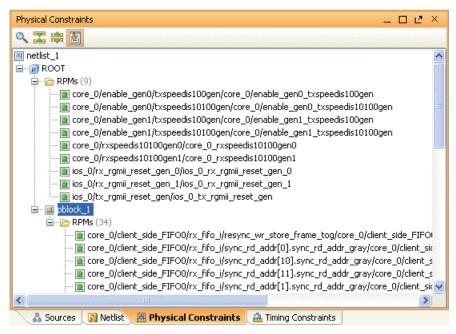

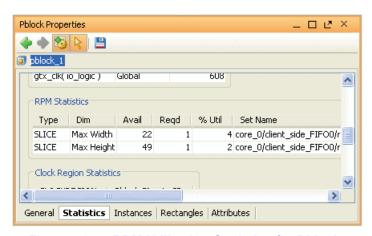

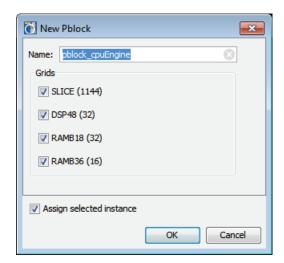

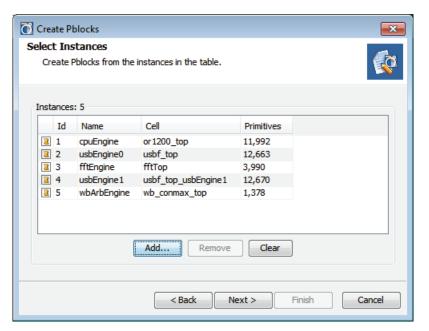

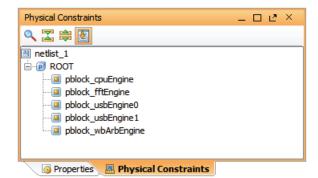

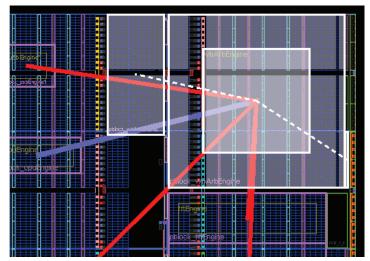

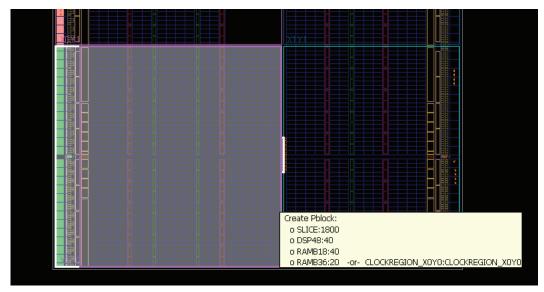

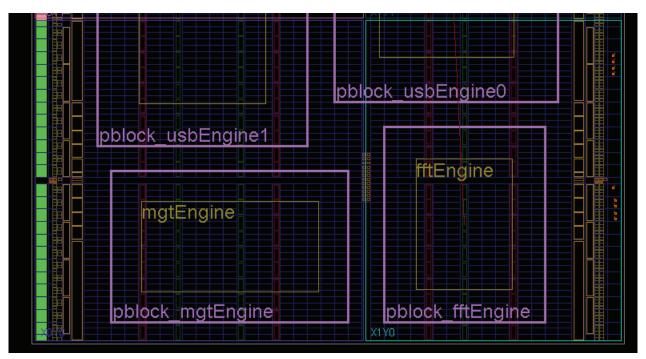

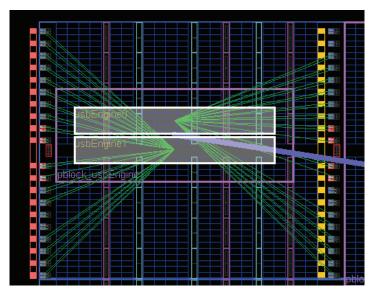

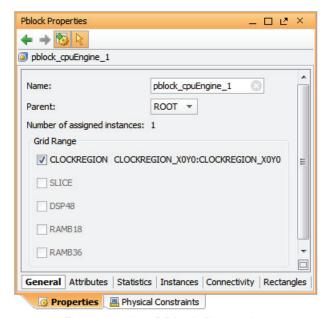

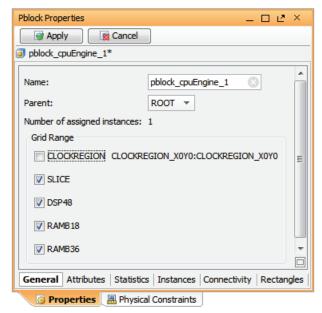

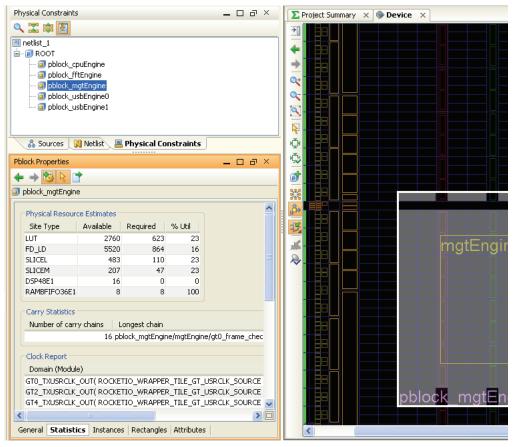

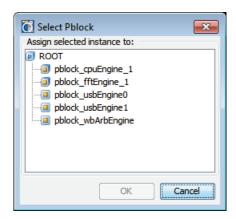

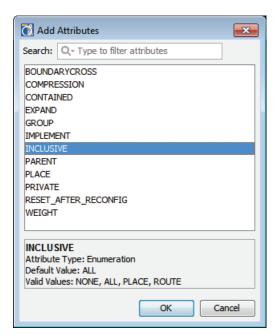

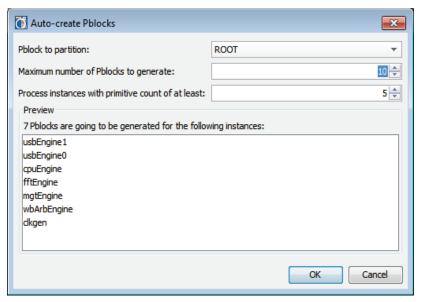

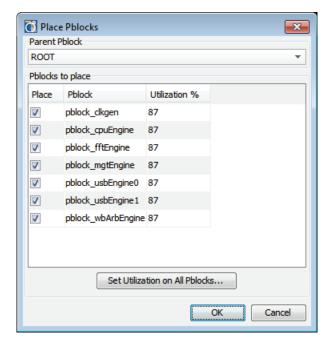

| Working with Pblocks                              | 303 |

| Configuring Pblocks                               | 312 |

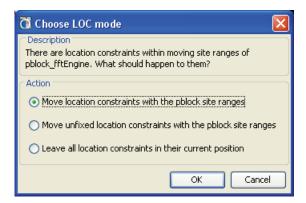

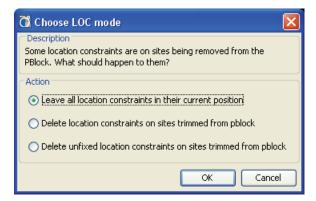

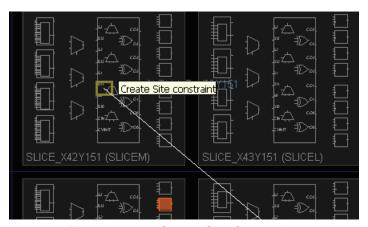

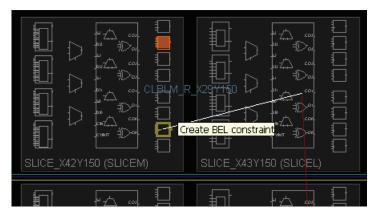

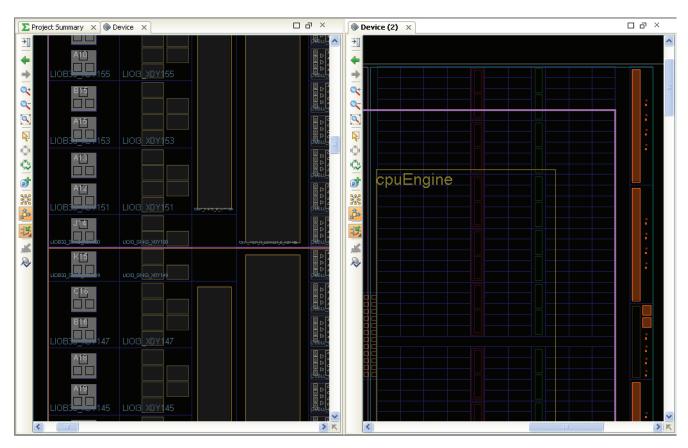

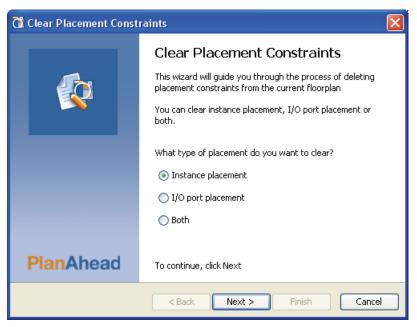

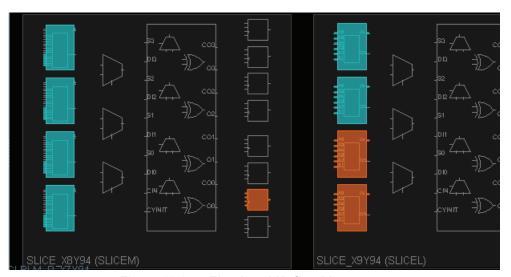

| Working with Placement LOC and BEL Constraints    | 324 |

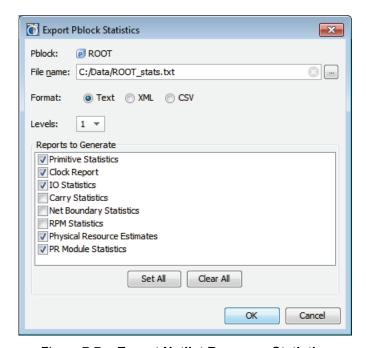

| Exporting Data from PlanAhead                     | 332 |

| Chapter 11: Analyzing Implementation Results      |     |

| Opening the Implemented Design                    | 335 |

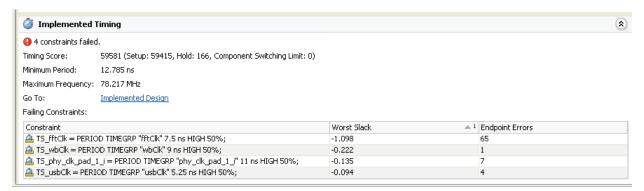

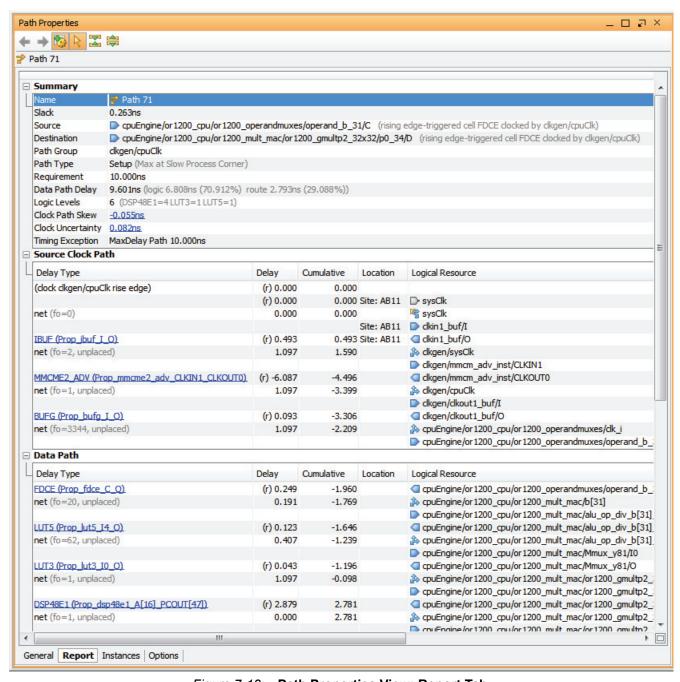

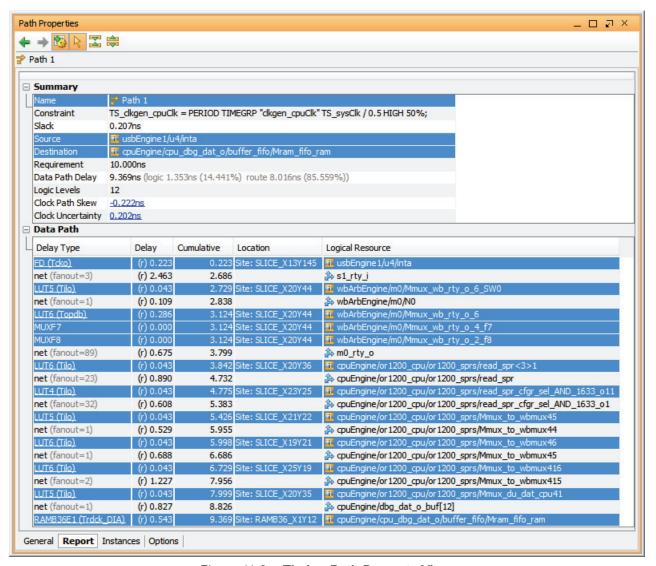

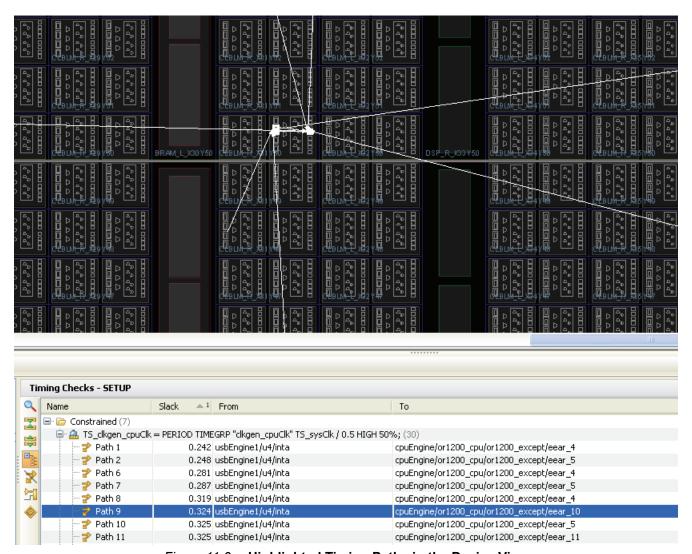

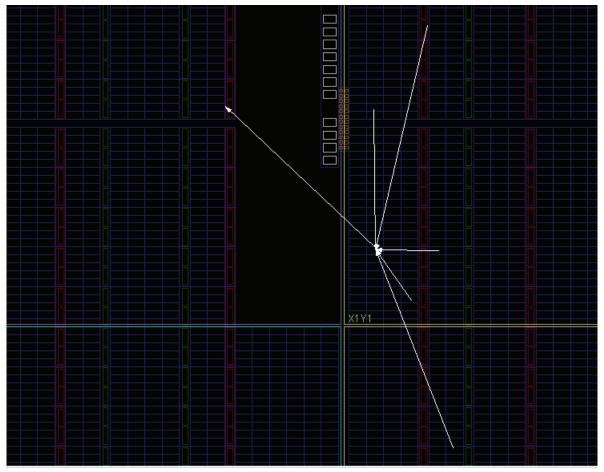

| Analyzing Timing Results                          | 338 |

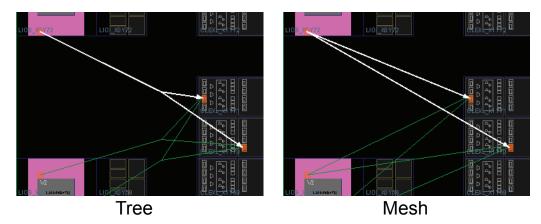

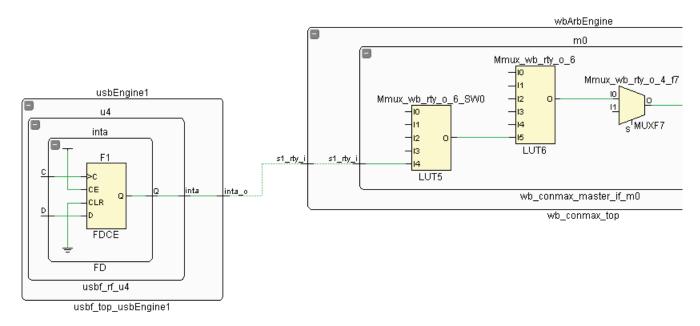

| Exploring Logic Connectivity                      | 346 |

| Locking Placement for Future Implementation Runs  | 350 |

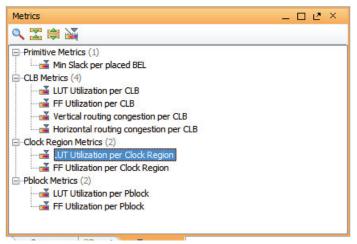

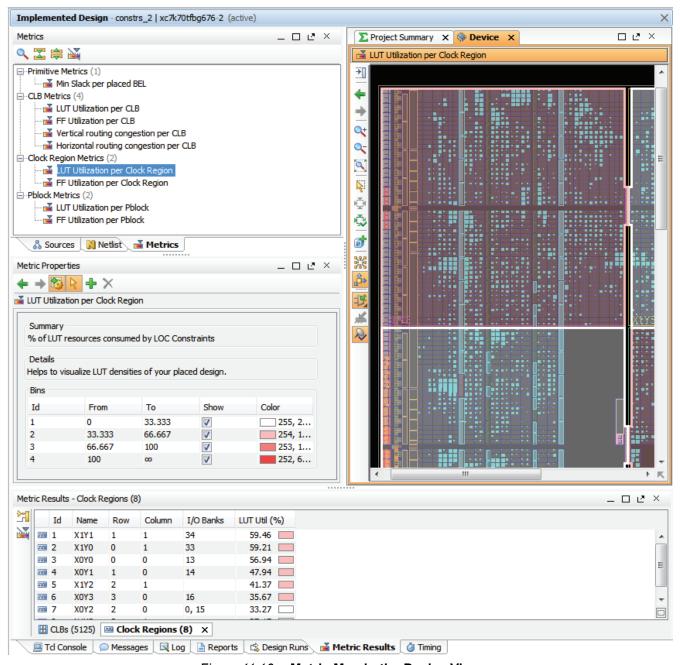

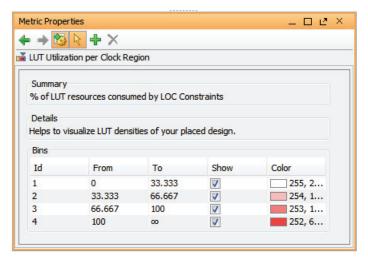

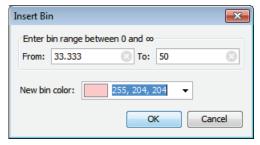

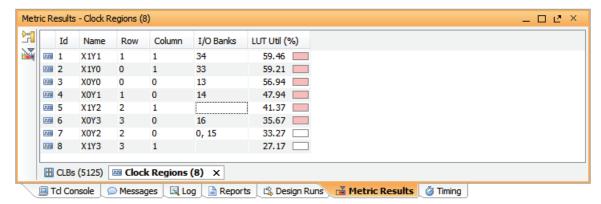

| Displaying Design Metrics                         | 351 |

| Performing Timing Simulation                      | 354 |

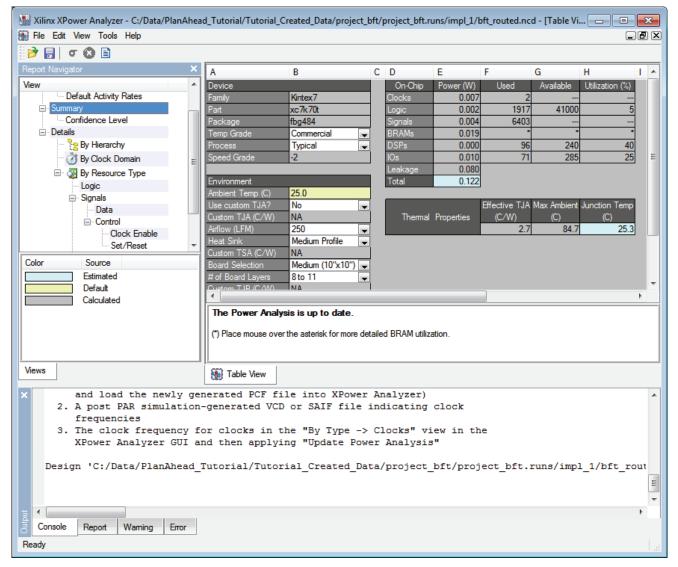

| Analyzing Power Distribution with XPower Analyzer | 362 |

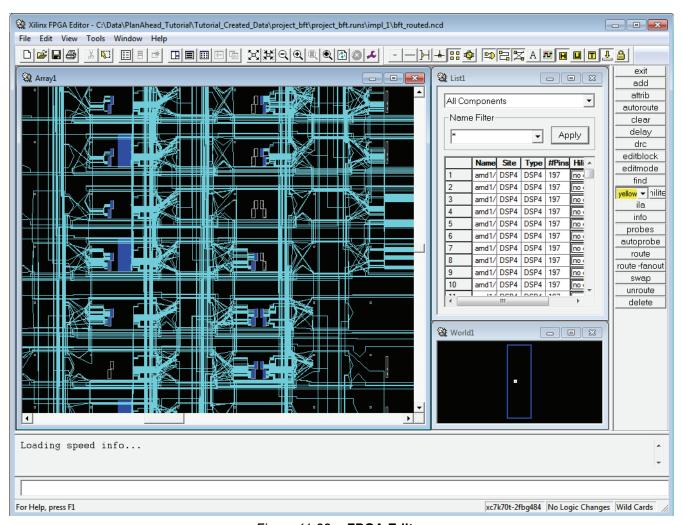

| Launching FPGA Editor                             | 363 |

| Chapter 12: Programming and Debugging the Design  |     |

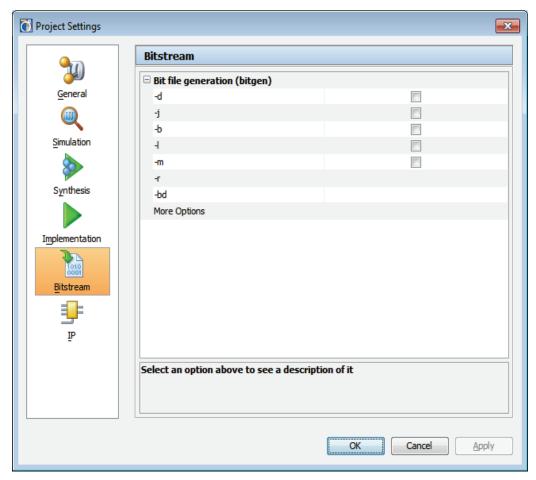

| Generating Bitstream Files                        | 365 |

| Debugging the Design with ChipScope               | 366 |

| Launching ChipScope Pro Analyzer                  | 375 |

| Launching iMPACT                                  | 375 |

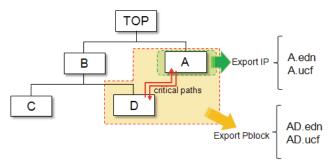

| Chapter 13: Using Hierarchical Design Techniques  |     |

| Using Partitions                                  | 377 |

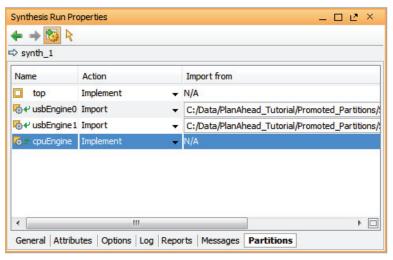

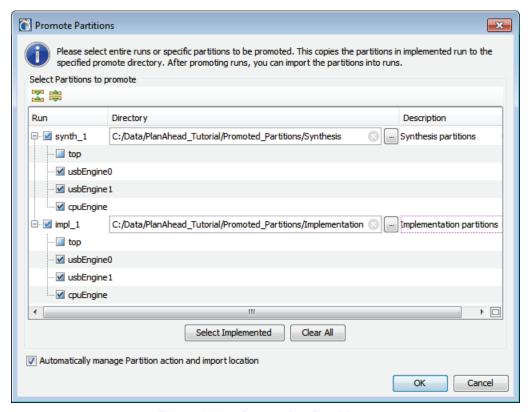

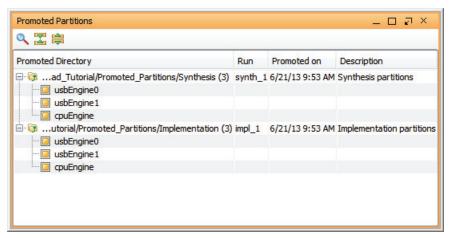

| Promoting Partitions                              | 381 |

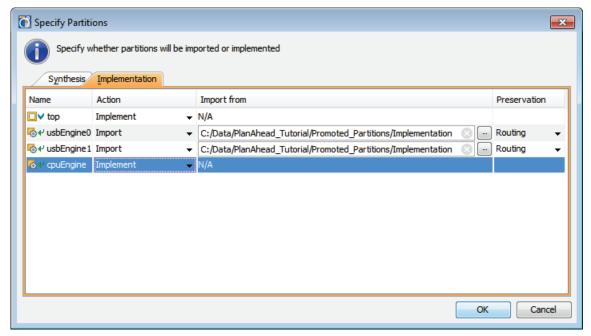

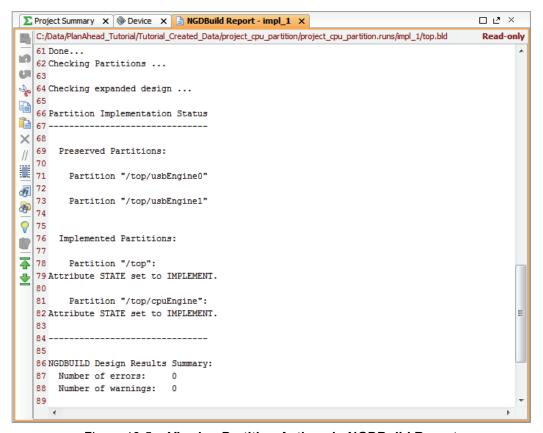

| Importing Partitions                              | 383 |

| Updating Sources                                  | 384 |

| Related Methodologies                             | 384 |

| Chapter 14: Tcl and Batch Scripting               |     |

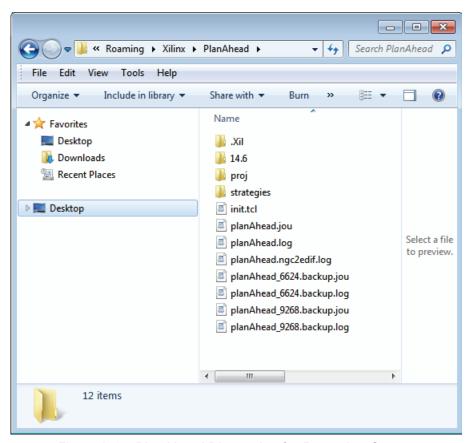

| Tcl Journal Files                                 | 385 |

| Tcl Help                                          | 385 |

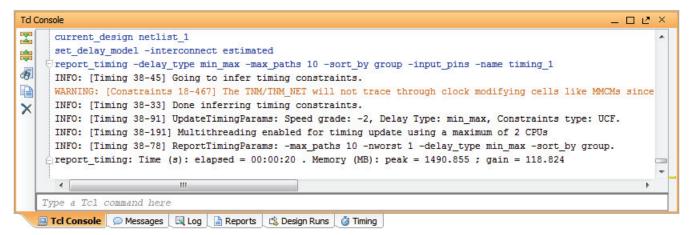

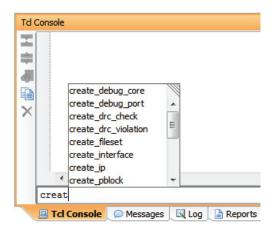

| Tcl Console                                       | 386 |

| Invoking the Plan Ahead Software                  | 387 |

| General Tcl Syntax Guidelines                                | 388 |

|--------------------------------------------------------------|-----|

| First Class Tcl Objects and Relationships                    | 391 |

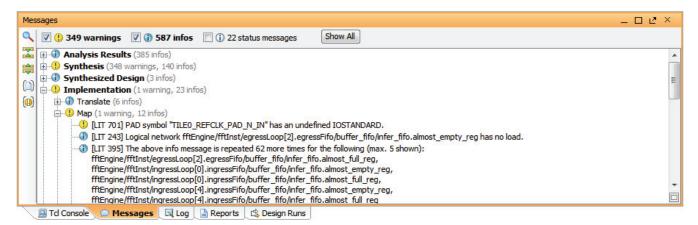

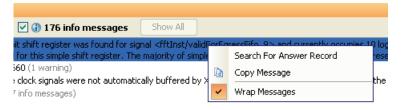

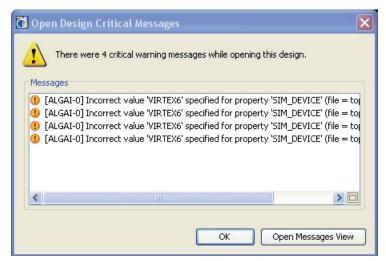

| Errors, Warnings, Critical Warnings, and Info Messages       | 395 |

| Tcl References                                               | 396 |

|                                                              |     |

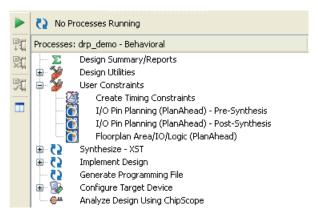

| Chapter 15: Using PlanAhead With Project Navigator           |     |

| PlanAhead Processes within Project Navigator                 | 397 |

| Appendix A: PlanAhead Input and Output Files                 |     |

| Input Files                                                  | 403 |

| I/O Port Lists (CSV) File Format                             | 404 |

| Outputs for Reports                                          | 407 |

| Outputs for Environment Defaults                             | 409 |

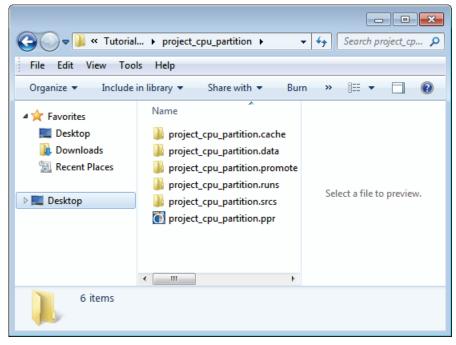

| Outputs for Project Data                                     | 410 |

| Outputs for ISE Implementation                               | 412 |

| Appendix B: PlanAhead DRCs                                   |     |

| RTL DRCs: Power and Performance                              | 115 |

| Floorplanning DRCs                                           |     |

| I/O Port and Clock Logic and Placement DRC Rule Descriptions |     |

| 2 0 1 0 1 0 1 0 1 0 1 1 1 1 1 1 1 1 1 1                      |     |

| Appendix C: Installing Releases with XilinxNotify            |     |

| PlanAhead Release Strategy                                   | 425 |

| Running XilinxNotify                                         | 425 |

| XilinxNotify Network Installations.                          | 425 |

| Appendix D: Configuring SSH Without Password Prompti         | na  |

| Setting Up SSH Key Agent Forward                             | _   |

| setting op som key rigent for ward                           | 72/ |

| Appendix E: Additional Resources                             |     |

| Xilinx Resources                                             | 429 |

| Hardware Documentation                                       | 429 |

| ChipScope Documentation                                      | 430 |

| EDK Documentation                                            | 430 |

| ISE Documentation                                            | 430 |

| System Generator for DSP Documentation                       | 431 |

| Partial Reconfiguration Documentation                        | 432 |

| Application Notes                                            |     |

| PlanAhead Documentation                                      | 432 |

| Zynq Documentation                                           | 433 |

| IP Documents                                                 | 433 |

### About the PlanAhead Tool

The Xilinx® PlanAhead™ tool is a design tool for the entire FPGA design and implementation cycle.

For information about Xilinx tool installation and new features, see the following documents cited in Appendix E, Additional Resources:

- Xilinx Design Tools: Installation and Licensing Guide (UG798)

- Xilinx Design Tools: Release Notes Guide (UG631)

- Known Issues for PlanAhead (AR40512)

#### About PlanAhead Software

The PlanAhead tool is a design and analysis product that provides an environment for the entire FPGA design and implementation process. The PlanAhead tool is integrated with:

- Xilinx ISE® Design Suite synthesis and implementation tools

- System Generator for DSP design

- Xilinx Embedded Development Kit (EDK)

- Xilinx Synthesis Technology (XST) tool

- CORE Generator<sup>TM</sup> tool

- ChipScope™ Pro debugging tool

- ISE Simulator (ISim) tool

- XPower Analyzer tool

- FPGA Editor tool

- iMPACT device programming tool

The PlanAhead tool lets you improve circuit performance by defining and analyzing the Register Transfer Level (RTL) sources in the design, synthesized netlists, and implementation results. You can experiment with different implementation options, refine timing constraints, and apply physical constraints with floorplanning techniques to help improve design results. Early estimates of resource utilization, interconnect delay, power consumption, and routing connectivity can assist with appropriate logic design, device selection and floorplanning.

The PlanAhead tool includes a hierarchical data model that enables an incremental design capability referred to as Design Preservation. By partitioning the design, unchanged modules can be preserved, providing consistent results and in some cases reduced runtimes.

With appropriate licensing, the PlanAhead tool also provides access to the Partial Reconfiguration design application. See Chapter 13, Using Hierarchical Design Techniques, for an overview of these advanced design techniques.

You can use the PlanAhead tool as a stand-alone application, or launch it for specific purposes from the ISE software. A subset of features is available when launched from Project Navigator; this subset is called ISE Integration Mode. Refer to Chapter 15, Using PlanAhead With Project Navigator, for more information about integration with Project Navigator.

#### **Using the PlanAhead Tool**

Use the PlanAhead tool to:

- Manage the design data flow with a push button run process from RTL development through bitstream generation.

- Perform RTL design and analysis using an Elaborated Design.

- Perform behavioral and timing simulation using the integrated Xilinx ISim tool.

- Export I/O Buffer Information Specification (IBIS) models.

- Customize and implement IP using the integrated CORE Generator tool.

- Configure and launch multiple synthesis and implementation runs.

- Perform I/O pin planning.

- Manage constraints and perform floorplanning.

- Estimate the resource utilization, timing, and power consumption.

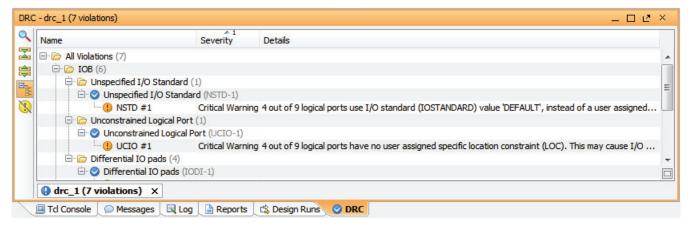

- Perform Design Rule Checks (DRCs).

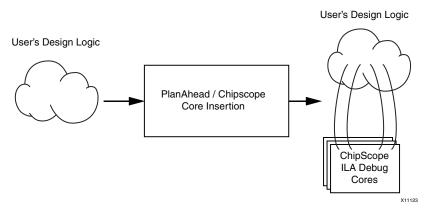

- Debug core insertion and implementation with the ChipScope debugging tool.

- Perform device configuration and file generation using the iMPACT tool.

- Analyze implementation results.

- Launch programming and design verification tools.

- Work with third party tools such as:

- Synplify Pro® FPGA synthesis software from Synopsys®

- Mentor Graphics® ModelSim or Questa® Advanced Simulator tool

- Precision® synthesis from Mentor Graphics

#### Project Creation and Management

The PlanAhead tool provides a variety of options for creating and managing FPGA design projects, and creating different constraint sets to explore design variations. See Chapter 3, Working with Projects.

#### RTL and IP Design

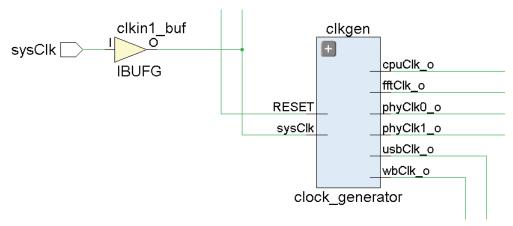

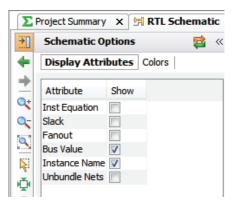

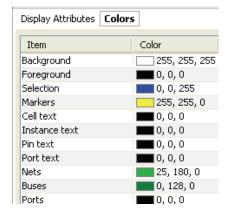

The PlanAhead tool Elaborated Design environment lets you create and manage RTL source files. You can customize and implement IP through integration with the CORE Generator tool. In addition to creating and managing design source files, the PlanAhead tool provides RTL source file elaboration enabling RTL logic exploration, an RTL Schematic Viewer, a set of RTL DRCs, and RTL-based resource and power estimation. For more information, see Chapter 5, Elaborated RTL Design.

#### **Design Simulation**

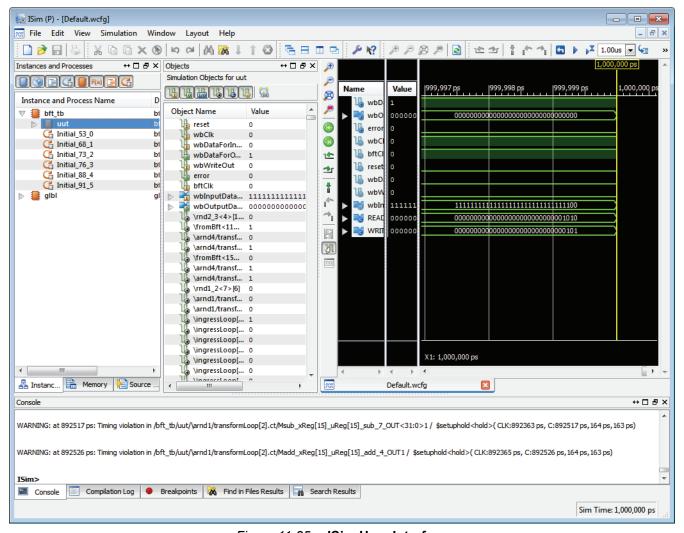

The PlanAhead tool also lets you launch Xilinx ISim to perform behavioral simulation of designs, and full timing simulation of implemented designs.

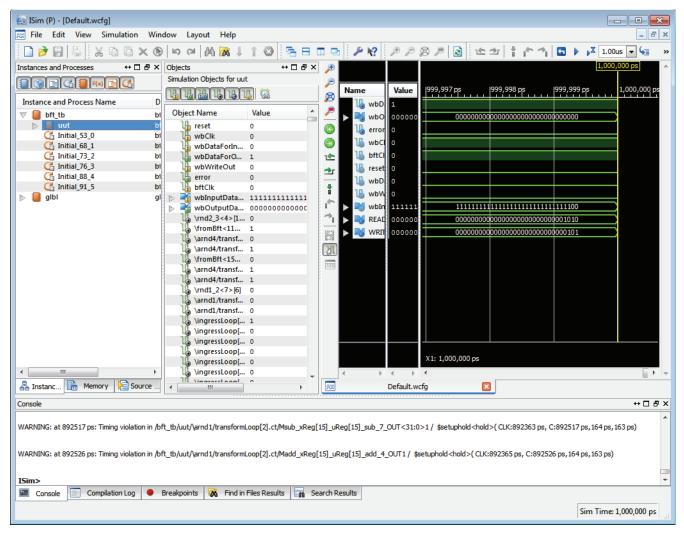

The PlanAhead tool prepares the required simulation executables and launches the ISim Graphical User Interface (GUI) to allow you to simulate the design, add and view signals in the waveform viewer, and examine and debug the design as needed. For more information, see:

- Chapter 5, Elaborated RTL Design for information about Behavioral simulation.

- Chapter 11, Analyzing Implementation Results for Timing simulation.

#### Synthesis and Implementation

The PlanAhead tool includes a synthesis and implementation environment supporting multiple synthesis and implementation runs using different physical or timing constraints, and different tool options to help complete routing and achieve timing closure. The synthesis and implementation runs can be queued to launch sequentially or simultaneously with multi-processor machines using the Xilinx ISE synthesis and implementation software.

- Chapter 6, Synthesizing the Design describes how to use synthesis.

- Chapter 9, Implementing the Design describes how to use implementation.

#### **Design Analysis and Constraints Definition**

The PlanAhead tool enables analyzing the design at each stage of the design process. Resource, timing, and power estimations along with DRCs let you experiment with various devices, constraints, and synthesis and implementation options to achieve desired results.

After implementation you can launch the FPGA Editor and XPower Analyzer tools directly from the PlanAhead tool for a detailed look at the implemented FPGA

These features are available both before and after implementation by analyzing the synthesized design or the implemented design results. For more information, see:

- Chapter 7, Synthesized Design Constraints and Analysis

- Chapter 11, Analyzing Implementation Results

#### Pin Planning

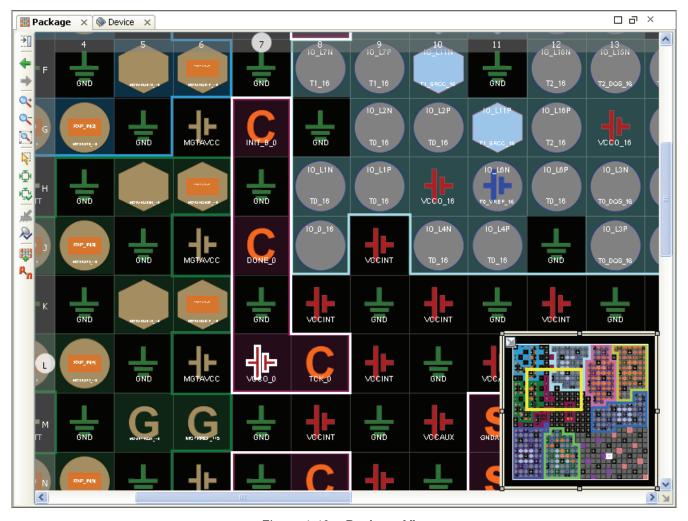

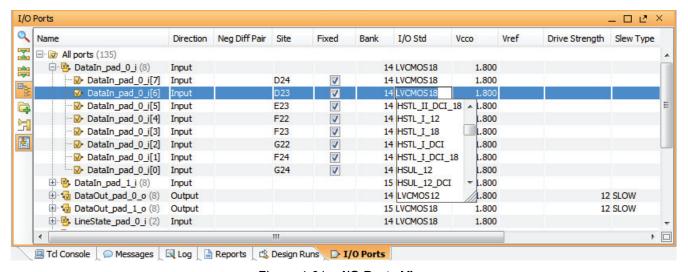

The PlanAhead tool provides an I/O Planning view to define and analyze the device I/O requirements. It supports creating and assigning I/O ports to physical package pins. This lets you define an I/O pinout configuration that satisfies the requirements of both the Printed Circuit Board (PCB) and the Field Programmable Gate Array (FPGA) designers. Chapter 8, I/O Pin Planning contains more information about I/O pin planning,

#### Floorplanning

The PlanAhead tool supports a floorplanning methodology that lets you group and constrain related logic to ensure shorter interconnect lengths with less delay, and to ensure more predictable implementation results. You can floorplan a design by creating physical block (Pblock) locations to constrain logic placement, or by locking individual logic objects to specific device sites. See Chapter 10, Floorplanning the Design and *Floorplanning Methodology Guide (UG633)*, cited in Appendix E, Additional Resources, for more information about floorplanning.

#### Programming and Debugging Designs and ChipScope Integration

The PlanAhead tool is integrated with the Xilinx ChipScope debugging tool, which lets you add debugging cores to your design.

After implementation, you can access the ISE tools to generate bitstream files, and launch the iMPACT and ChipScope Analyzer tools directly from within the PlanAhead tool. See Chapter 12, Programming and Debugging the Design.

#### Hierarchical Design, Design Preservation, and Partial Configuration

The PlanAhead tool provides some advanced hierarchical design features to support team design, design preservation, and partial reconfiguration methodologies. See Chapter 13, Using Hierarchical Design Techniques.

The *Hierarchical Design Methodology Guide (UG748)*, cited in Appendix E, Additional Resources, more completely describes the hierarchical design process.

#### Tcl Commands and Batch Scripting

For information about the syntax of Tool Command Language (Tcl) commands and batch options in the PlanAhead tool, see Chapter 14, Tcl and Batch Scripting.

For a reference to the Tcl commands supported by the PlanAhead tool, see *PlanAhead Tcl Commands Reference Guide (UG789)*, cited in Appendix E, Additional Resources.

#### Using PlanAhead Software with the ISE Project Navigator Environment

The PlanAhead tool is integrated with the Project Navigator software tool to provide an environment for improving your design results throughout the design flow.

Project Navigator automatically launches the PlanAhead tool at the following design steps:

- Pre-Synthesis:

- I/O pin planning

- Post-Synthesis:

- I/O pin planning

- Floorplan Area/IO/logic

- Post-Implementation:

- Analyze Timing and Floorplan design

See Chapter 15, Using PlanAhead With Project Navigator for information about ISE Integration mode.

#### Input and Output Files

The PlanAhead tool accepts a variety of input files and creates a variety of output file types and formats. See Appendix A, PlanAhead Input and Output Files for descriptions of the input and output files.

#### Design Rule Checks

The PlanAhead tool Design Rule Checks (DRCs) are listed in Appendix B, PlanAhead DRCs.

#### PlanAhead Software Terminology

For definitions of the terminology used in this Guide, see *Xilinx Glossary*, cited in Appendix E, Additional Resources.

#### Accessing Updates

Xilinx uses a XilinxNotify utility that notifies you when there are updates available. See Appendix C, Installing Releases with XilinxNotify for more information.

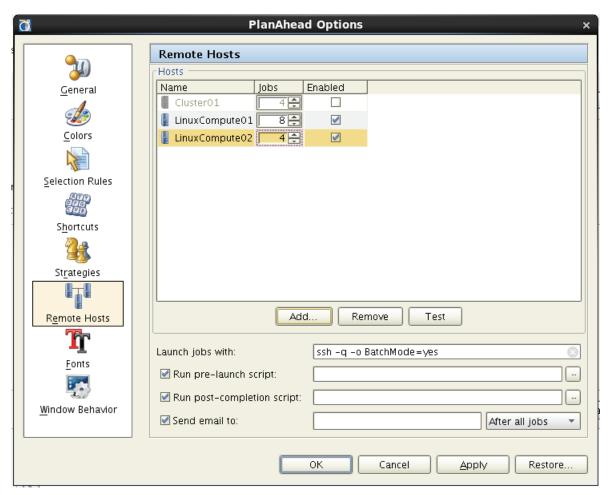

#### Configuring Multiple Linux Hosts

The multiple host capabilities for executing PlanAhead synthesis and implementation runs use the Linux Secure Shell (SSH). Before configuring multiple hosts in the PlanAhead tool, configure SSH so you are not prompted for a password each time you log in to a remote computer.

For more information, see Appendix D, Configuring SSH Without Password Prompting.

#### Additional Resources

Appendix E, Additional Resources contains links to all documents referenced in this guide. If you are using at a printed copy of this guide, the full URL to the referenced document is provided.

#### Launching the PlanAhead Tool

You can invoke the PlanAhead tool from any directory; however, running it from a project directory is advantageous because the PlanAhead log and journal files are written to the launch directory, making the project log files easy to find.

You can launch the PlanAhead tool and run the tools using different methods, or modes of operation, depending on your design preference. For example, you can choose to run the PlanAhead tool interactively from the command line using Tcl shell mode, or interactively with a graphical editor using the PlanAhead GUI. You can also run the PlanAhead tool automatically in batch mode, specifying a Tcl script to complete the design.

For help on the various modes and options for running the PlanAhead tool, you can enter the following from the Linux or Windows command line:

```

planAhead -help

```

#### Launching the PlanAhead tool Tcl Shell

Use the following command to invoke the interactive Tcl shell either at the Linux command prompt or within a Windows Command Prompt window:

```

planAhead -mode tcl

```

#### Launching the PlanAhead tool Using a Batch Tcl Script

You can run the PlanAhead tool in batch mode by supplying a Tcl script when invoking the tool. Use the following command either at the Linux command prompt or within a Windows Command Prompt window:

```

planAhead -mode batch -source <your_Tcl_script>

```

**Note:** When working in batch mode, the PlanAhead tool exits after running the specified script.

#### Launching the PlanAhead GUI

To launch the PlanAhead from the Windows Start menu, select the following command:

```

Start > All Programs > Xilinx Design Tools > ISE Design Suite 14.x >

PlanAhead > PlanAhead

```

**Note:** You can also double-click the PlanAhead tool shortcut icon on your desktop, or double-click the PlanAhead project file (.PPR) from the directory where the file resides.

The PlanAhead tool opens to the Getting Started Page as shown in Figure 1-1, page 13.

The Getting Started page assists you with creating or opening projects as well as viewing the documentation. To display the Getting Started page, close all open projects.

#### Launching the PlanAhead GUI from the Command Line

From the Windows or Linux command prompt, enter the following command:

```

planAhead -mode gui

-or-

planAhead

```

**Note:** These two commands are the same. If you need help, type planAhead -help.

#### Starting the PlanAhead GUI from the Tcl Shell

To launch the PlanAhead tool GUI when running from the Tcl shell, enter the following command at the Tcl command prompt:

```

start_gui

```

You can exit the GUI and return to the Tcl shell using the following command:

```

stop_gui

```

Figure 1-1: PlanAhead Software Getting Started Page

#### Using the Getting Started Page

The Getting Started page displays with the following options:

- Create New Project: Invokes the New Project wizard which lets you create any type of PlanAhead design project.

- **Open Project:** Invokes a browser enabling you to open any PlanAhead design project file (.ppr), or ISE Design Suite project file (.xise).

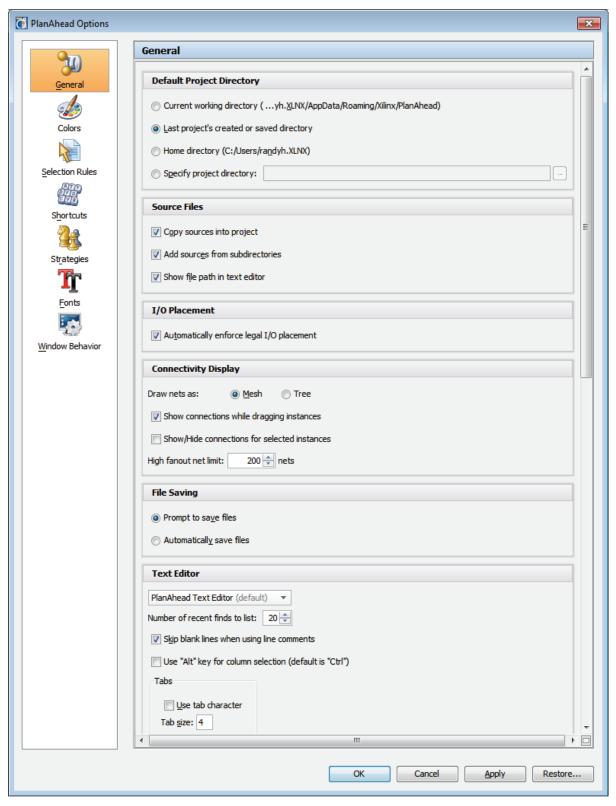

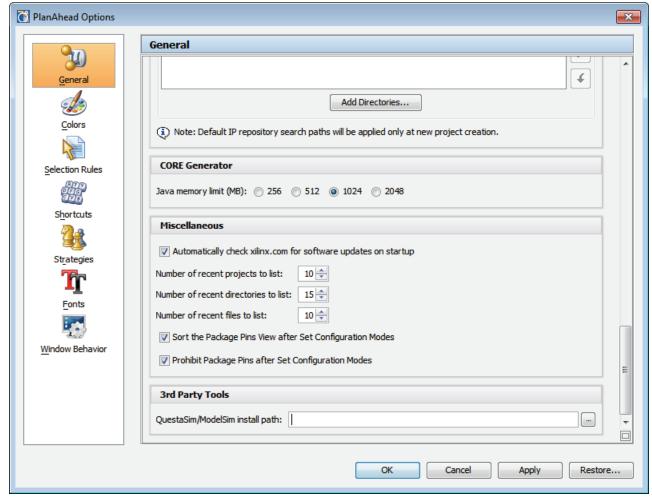

- Open Recent Project: Displays the last 10 previously-opened projects. Ten is the default; to change this number, use Tools > Options > General). The PlanAhead tool checks to ensure the project data is available before displaying the projects.

- Open Example Project: Provides four sample design projects:

- **BFT Core:** A small RTL project BFT Core (bft.ppr)

- **CPU (HDL):** A larger RTL project CPU (HDL)

- **CPU (Synthesized):** A netlist-based project CPU (synthesized)

- Wave (HDL): An IP example with three embedded IP cores from CORE Generator, Wave (HDL). You can use this design as a reference project to see how you can use IP cores with PlanAhead design projects.

To open or download the PlanAhead tool documentation, click the documentation links to launch a PDF viewer or website download location.

**Note:** The PlanAhead tool installs with a placeholder PDF file for the User Guide. In that file, you are guided to a web URL to download the latest document. There are simple installation instructions to enable the link to then invoke the full local copy of the User Guide when selected.

- **Release Notes Guide:** A web link to the Release Notes for a given release.

- User Guide: A link to this manual.

- Methodology Guides: A web link to Xilinx methodology guides.

- PlanAhead Tutorials: A web link to Xilinx tutorials and supporting design data.

#### **Command Line Options**

The PlanAhead tool has several command line options. To view the PlanAhead tool command line options, type the following command at the command prompt:

```

# planAhead -help

```

A help menu displays in the shell window.

#### Using a Startup Tcl Script

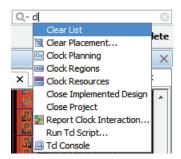

Use the **Tools > Run Tcl Script** command to run a script.

You can copy the PlanAhead tool Tcl commands from the planAhead.jou file, or from the Tcl console, to create startup scripts. Figure 1-2 shows a code snippet from a Tcl script.

```

#------

create_project project_1 {C:\Data\PlanAhead_Designs\PlanAhead_Tutorial\Tutorial_Created_Data\project_1}

set_property design_mode RTL [get_property srcset [current_run]]

import_files -force -norecurse {C:\Data\PlanAhead_Designs\12_demo\Sources\Therm}

set_property library work [get_files -of_objects [get_property srcset [current_run]] {{C:\Data\PlanAhead}

import_files -fileset [get_property constrset [current_run]] -force -norecurse {C:\Data\PlanAhead_Desig

set_property top therm [get_property srcset [current_run]]

set_property verilog_2001 true [get_property srcset [current_run]]

set_property verilog_uppercase false [get_property srcset [current_run]]

set_property loop_count 1000 [get_property srcset [current_run]]

launch_runs -runs synth_1 -jobs 1

launch_runs -runs impl_1 -jobs 1

close project

```

Figure 1-2: Example Tcl Script

For more information about the PlanAhead tool journal file, see Journal File (planAhead.jou and planAhead\_<id>.backup.jou), page 408. For more information about scripting and using the PlanAhead tool with Tcl, see Chapter 14, Tcl and Batch Scripting.

## The PlanAhead Tool Flow

You can use the PlanAhead<sup>TM</sup> tool at many places in the design flow. The flows described in this chapter correspond to the project types that can be created. Project types are described in more detail in Chapter 3, Working with Projects.

You have access to design analysis and constraint definition capabilities at each stage of the design flow, including elaborated Register Transfer Level (RTL) design, synthesized design, and any of the implemented design runs.

Design flows supported by the PlanAhead tool include:

- RTL to Bitstream Use the PlanAhead tool to manage the entire FPGA design process from RTL development, IP customization, synthesis and implementation through to programming the device. You can add Verilog and VHDL sources, previously defined and configured intellectual property (IP) cores, DSP modules from System Generator, embedded processor designs from EDK, and physical and timing constraints to a project. You can experiment with synthesis, simulation, and implementation options and constraints to help meet your design objectives.

- Synthesized Netlist to Bitstream The PlanAhead tool manages netlist designs from

implementation to device programming. You can add synthesized netlists, netlist-based IP

cores, and constraints to a project. You can experiment with implementation options and

constraints to help meet your design objectives.

- Device Exploration and I/O Pin Planning The PlanAhead tool provides an I/O Planning environment to analyze the device resources and visualize the relationship between the FPGA and system-level designs. Proper clocking and I/O planning can improve device performance and routability. Early I/O planning can also improve PCB routing, signal integrity, and the performance of the overall system. You can also migrate an I/O Pin Planning Project into an RTL Project, using the pin plan as the starting point for the top-level of the design.

- Analyze Implemented Design Results Use the PlanAhead tool to analyze implementation

results generated outside of the PlanAhead tool, such as in Xilinx ISE® Design Suite. You can

examine placement and timing results to explore design changes, timing adjustments, or

floorplanning to achieve timing closure.

- Partial Reconfiguration<sup>(1)</sup> The PlanAhead tool provides an environment to set up and manage partial reconfiguration projects. These designs require special features and project structure to manage reconfigurable modules. For more information, see the *Partial Reconfiguration User Guide (UG702)*, cited in Appendix E, Additional Resources.

<sup>1.</sup> Partial Reconfiguration is only available under special licensing.

#### **Design Flow**

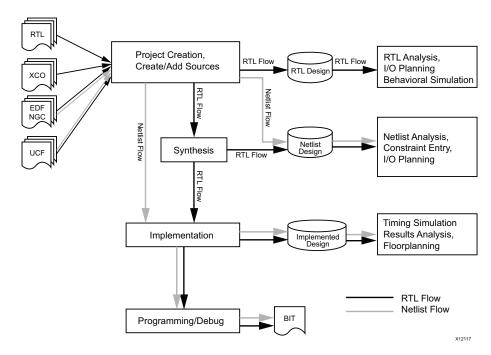

The PlanAhead design flow depends on the type of input file that you start with. This section describes the design flow and design tasks. Figure 2-1 shows the common design flows, and the input and outputs of the PlanAhead tool.

Figure 2-1: PlanAhead Design Flows

#### Project Creation and Management of Project Sources

The PlanAhead tool provides a wizard flow to facilitate project creation and the creation or addition of source files to the project. You can:

- Create projects specific to the type of flow and sources you are using

- Create new source files or add existing source files to the project

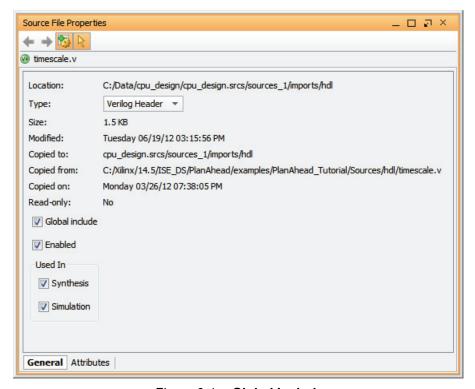

- Reference remote, write-protected files, or copy files into the local project folder

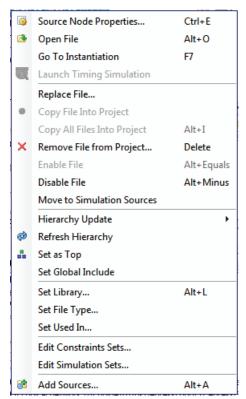

- Disable or enable source files within a project

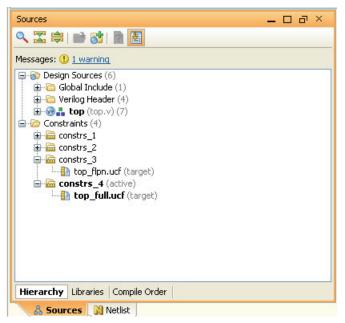

- Create constraint sets to experiment with various constraints options or devices

- Create simulation source sets for behavioral and timing simulation

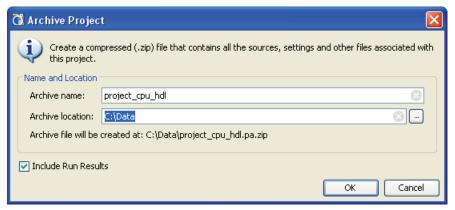

- Archive projects to create a backup or make a portable copy of the design

The PlanAhead tool project environment lets you create and store multiple variations of the design constraints within a single project. This allows for the creation of multiple RTL source versions, constraints sets, target devices, synthesized netlists, and implementation run results using various implementation strategies. As you modify the source files or launch design tools, the software monitors and displays design flow status.

#### RTL Development and Analysis

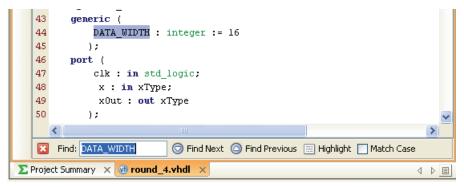

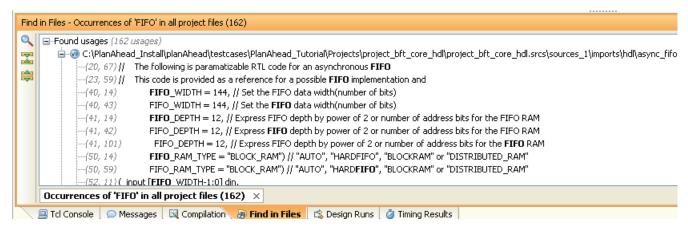

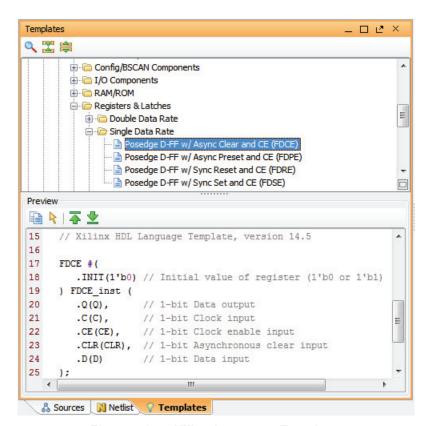

The PlanAhead tool includes an integrated text editor to create or modify source files. You can copy example logic constructs directly from the supplied Xilinx template library. The PlanAhead tool contains a Find in Files feature that lets you search these libraries using a variety of search criteria.

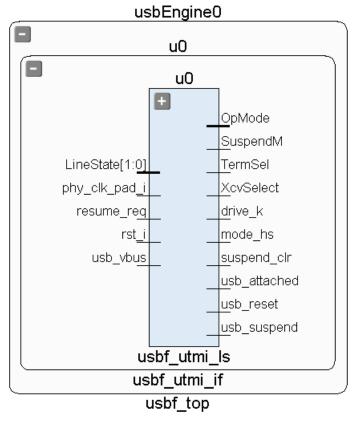

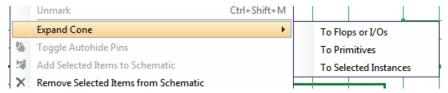

Opening an Elaborated Design elaborates the RTL source files and loads the RTL netlist automatically. The open Elaborated Design lets you check RTL structure, syntax, and logic definitions. Analysis and reporting capabilities include:

- RTL compilation validation and syntax checking

- Netlist and schematic exploration

- Design Rule Checks (DRCs)

- Behavioral simulation

- Resource utilization and power consumption estimation

- Early I/O pin planning is enabled using an RTL port list.

With a design open, selecting an object in one view will cross-select the object in other views, including instantiations and logic definitions within the RTL source files. Refer to Chapter 5, Elaborated RTL Design, for more information.

#### IP Customization and Implementation

Run the integrated CORE Generator<sup>TM</sup> tool to browse, customize, instantiate, implement, and automatically update IP.

#### Logic Synthesis

The PlanAhead tool lets you configure, launch, and monitor synthesis runs using the Xilinx® Synthesis Technology (XST) tool. Refer to Chapter 6, Synthesizing the Design, for more information.

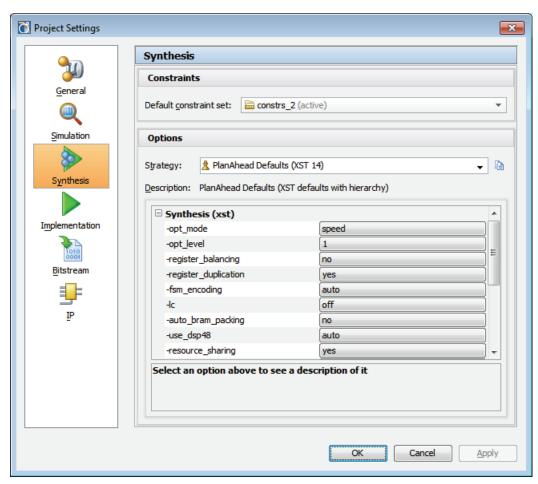

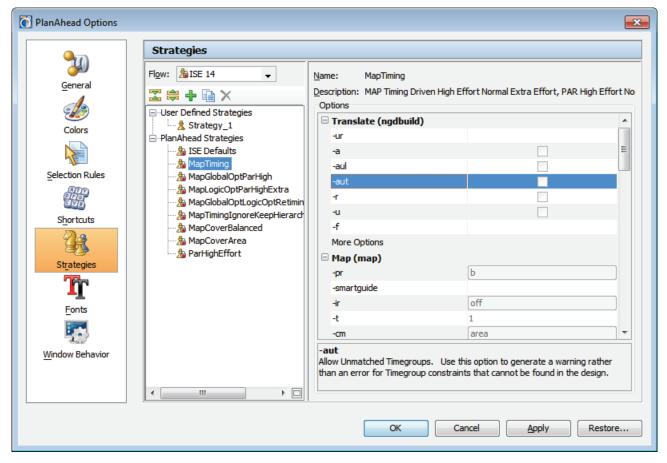

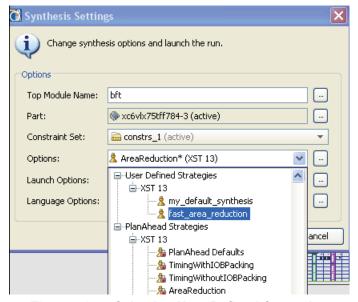

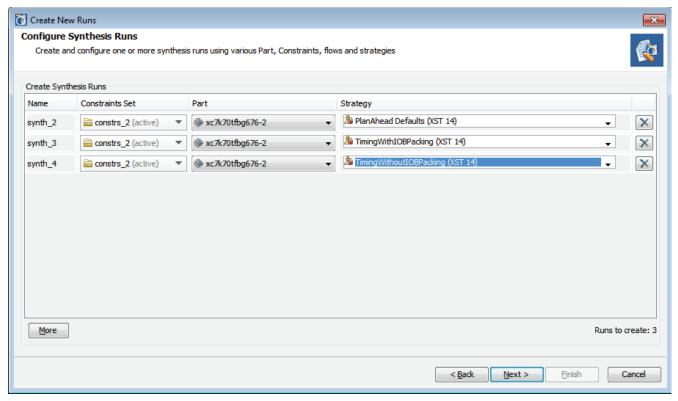

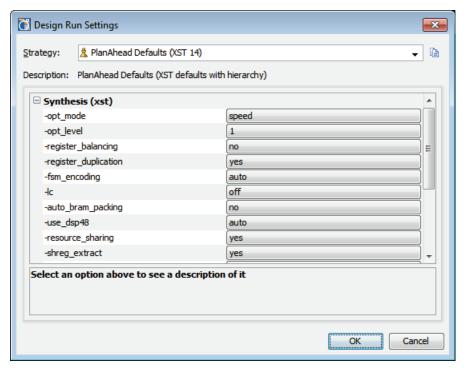

You can experiment with different synthesis options and create reusable *strategies* for Synthesis runs. For example, you could create strategies for power, performance, or area optimization.

The Synthesis run results display interactively, and the PlanAhead tool creates report files that you can access. Select synthesis Warnings and Errors from the Compilation Messages view to highlight the logic in the source files.

- You can launch multiple Synthesis runs simultaneously or serially.

- On a Linux system, you can launch runs locally or on remote servers.

When you have multiple Synthesis runs, those runs create multiple netlists that are stored within the PlanAhead tool project. The PlanAhead tool then lets you load the various versions of the netlist into the environment for analysis. After the netlist import, you can perform device and design analysis, and create constraints for I/O pin planning, floorplanning, and implementation.

The most comprehensive list of Design Rule Checks (DRCs) is available after a synthesized netlist is produced, when clock and clock logic are available for analysis and placement.

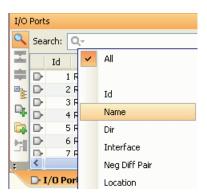

#### I/O Pin Planning

The PlanAhead tool provides an I/O pin planning environment that enables correct "by-construction" I/O port assignment either onto specific device package pins or onto internal die pads. The PlanAhead tool offers a variety of display views and tables in which to analyze and design

package and design I/O related data. Refer to Chapter 8, I/O Pin Planning, for more information.

You can:

- Examine the internal I/O connectivity to ensure proper data flow through the device as well as optimal access to internal device resources.

- Improve system performance by examining both the external and internal connectivity requirements and then making informed decisions.

- Use DRCs and Simultaneous Switching Noise (SSN) analysis to ensure compliance to connectivity requirements.

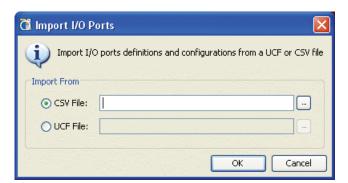

- Use a variety of source input formats to begin I/O pin planning including: CSV, UCF, RTL, or synthesized netlists.

When you use a synthesized netlist as the source, the DRC coverage improves substantially because often the clock logic dictates proper I/O assignment. The final I/O verification step is to run the complete design through the implementation tools.

#### **Netlist Analysis and Constraints Definition**

The PlanAhead tool has design analysis and constraints assignment capabilities. The design data is presented in different forms using cross-selecting and coordinating views.

The PlanAhead tool provides interactive graphical views of the internal die and external package with which you can analyze device resources and apply constraints. You can also apply and analyze timing and physical constraints.

Early timing analysis, including timing simulation, resource estimation, connectivity analysis, and DRCs help identify design issues prior to Implementation.

#### Implementation

The PlanAhead tool lets you configure, launch, and monitor implementation *runs* using the ISE® Design Suite.

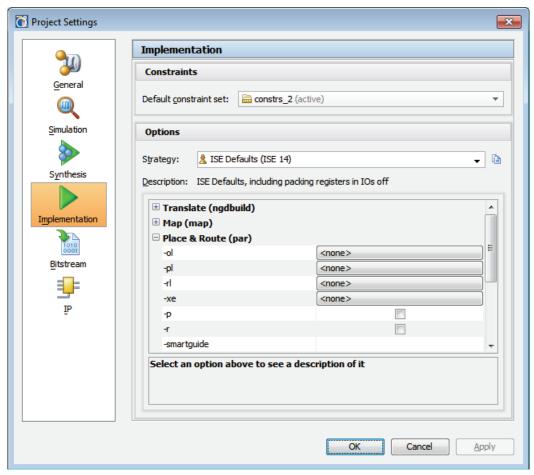

You can experiment with different implementation options and create reusable *strategies* for implementation runs. As an example, you can create strategies for quick runtimes, performance, or area optimization.

The implementation run results display interactively, and report files are accessible.

Also, you can launch multiple implementation runs either simultaneously or serially: when using the Linux operating system you can use remote servers. You can create *Constraint Sets* so you can experiment with various logical constraints, physical constraints, or alternate devices.

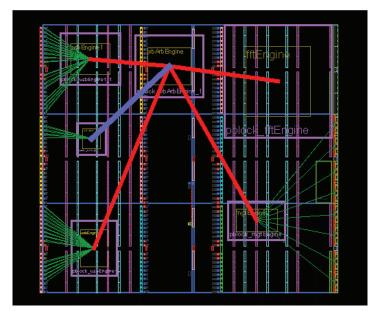

#### Results Analysis and Floorplanning

Load the various run results interactively for analysis and floorplanning. The capabilities in the Implemented Design are described in:

- Chapter 7, Synthesized Design Constraints and Analysis

- Chapter 11, Analyzing Implementation Results

You can import results from any run that is launched from the PlanAhead tool.

When you open an Implemented Design, the original netlist, constraints, and implementation results are loaded into the Results Viewer. You can open multiple designs simultaneously. You can also launch the ISE Simulator (ISim) for timing simulation, XPower Analyzer, and FPGA Editor tools directly from the PlanAhead tool for further design analysis.

#### **Device Programming**

You can create programming bitstream files for any completed implementation run. Bit file generation options are configurable. Launch the iMPACT tool to configure and program the part.

#### Design Verification and Debug

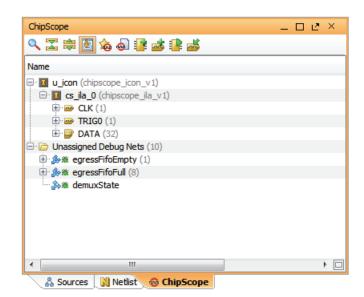

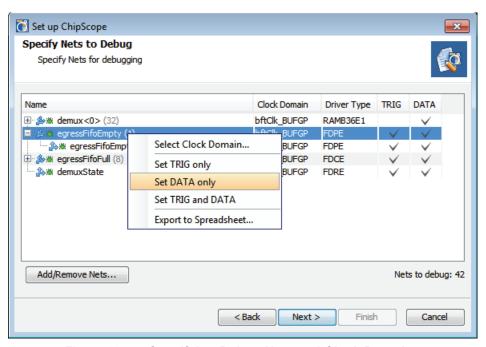

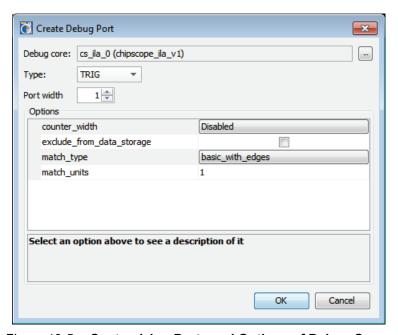

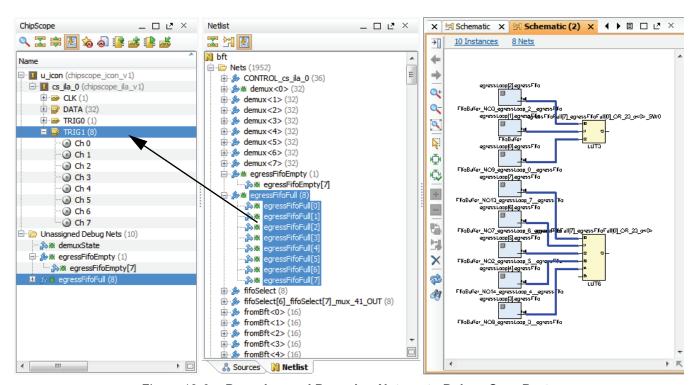

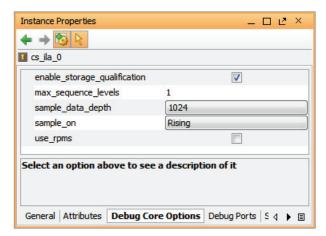

You can configure and implement ChipScope<sup>TM</sup> Pro Analyzer tools and IP cores, such as the Integrated Logic Analyzer (ILA) and Integrated Controller (ICON), in the Synthesized Design, and select and configure the required probe signals into the cores. You can launch the ChipScope Analyzer tool on any run that has a completed bitstream file.

You can launch the ChipScope Analyzer tool directly from the PlanAhead tool for further analysis of the routing or device resources.

#### **User Models**

The PlanAhead tool provides a Graphical User Interface (GUI) with "layered complexity." It provides an intuitive environment for new or casual users and also provides access to the more advanced features. By default, the PlanAhead tool opens with a push button flow suitable for users who do not require more advanced analysis and floorplanning features. The flow is controlled by a view called the *Flow Navigator*, described in Understanding the Flow Navigator, page 19.

#### **Basic User Flow**

The PlanAhead tool lets you execute the entire development cycle using the run buttons in the PlanAhead tool Flow Navigator. You can traverse the FPGA development process front-to-back, beginning with importing source files, synthesizing design logic, implementing synthesized netlists, analyzing the results, generating bitstreams, and launching programming and verification tools.

#### Advanced User Features

The PlanAhead tool provides a series of analysis environments at each stage of the design flow for advanced design configuration and analysis. You can load the Elaborated Design, Synthesized Design, and Implemented Design for analysis and constraint definition. These environments are described in Working with Designs, page 24.

The PlanAhead tool lets you create and store multiple variations of the design within a single project. This allows for the creation of multiple RTL source versions, constraints sets, target devices, synthesized netlists, and implementation run results using various implementation strategies. As you modify the source files or launch design tools, the software provides a design status.

You can configure, launch, and monitor multiple synthesis and implementation runs locally or on remote Linux servers. You can experiment with different command options, constraints, and devices.

#### Understanding the Flow Navigator

The Flow Navigator provides control over the major design process tasks, such as project configuration, synthesis, implementation, and bitstream creation. As these tasks are completed, you can open the resulting designs to analyze results and apply constraints by clicking **Open Elaborated Design**, **Open Synthesized Design**, or **Open Implemented Design** in the Flow Navigator. Each of these Designs displays a set of commonly used commands for the applicable phase of the design flow.

Available options depend on the status of the design. Inapplicable steps are greyed out until the appropriate design tasks are completed.

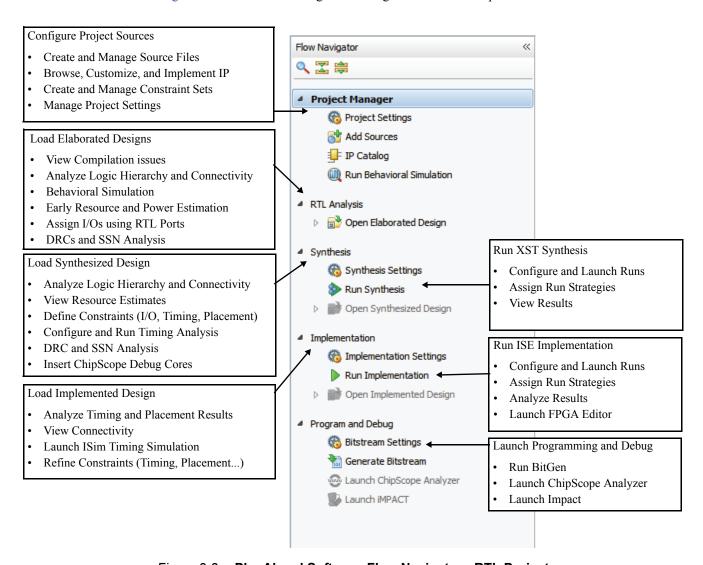

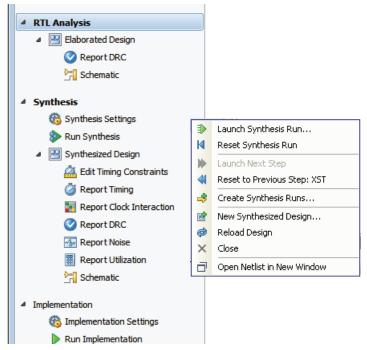

Figure 2-2 and Figure 2-3, page 21 illustrate how the Flow Navigator view is used to perform design tasks and to open the analysis environments at various stages of the design process.

#### Using the Flow Navigator with an RTL Project

Figure 2-2 illustrates the design flow using RTL sources as input to the PlanAhead tool.

Figure 2-2: PlanAhead Software Flow Navigator - RTL Project

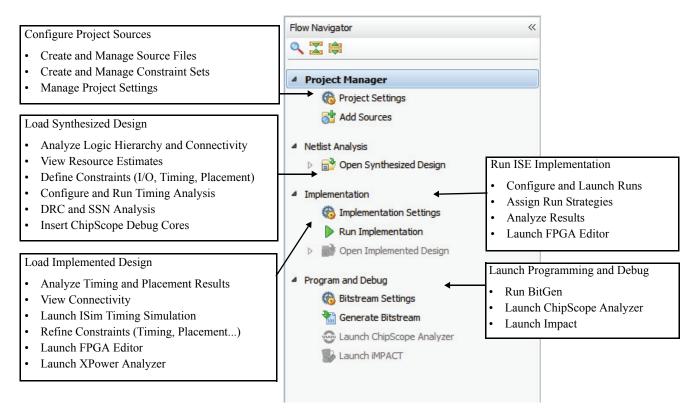

#### Using the Flow Navigator with a Synthesized Netlist Project

Figure 2-3 illustrates the design flow for synthesized netlist-based projects.

Figure 2-3: PlanAhead Software Flow Navigator - Synthesized Netlist Project

#### Launching Commands from the Flow Navigator

The Flow Navigator facilitates a push button flow by enabling synthesis and implementation to be run immediately after you add source files to a project. There is no need to open any of the Design environments to complete the design. The following subsections describe how to complete a design using the Flow Navigator.

#### Project Manager

When you open a project, the Project Manager opens by default. When you open the Project Manager, no design compilation is performed and no design data is loaded into memory. The Project Manager displays the sources, source properties, and a Project Summary view by default. This environment enables creating, importing, and managing source files and constraint sets. You can also use the Project Manager to browse, customize, and create IP from the Xilinx IP Catalog.

The Project Manager menu of the Flow Navigator contains the following commands:

Project Manager: Opens the Project Summary view of the current project. See Using the Project Summary view, page 84 for more information. Click the arrow icon to expand and collapse the menu of Project Manager commands.

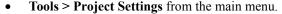

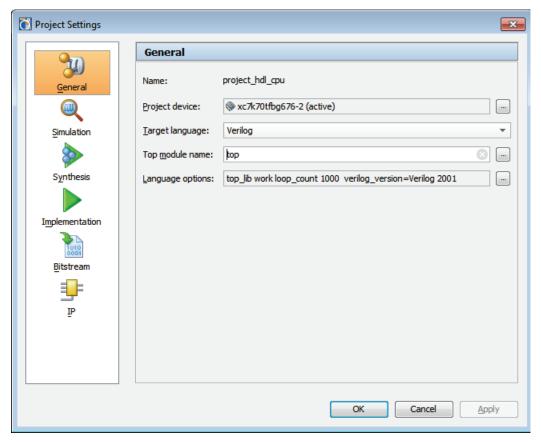

- Project Settings: Opens the Project Settings dialog box. Refer to Configuring Project Settings, page 88 for more information.

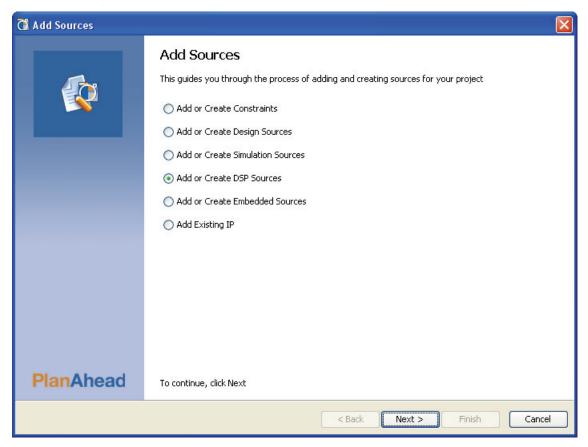

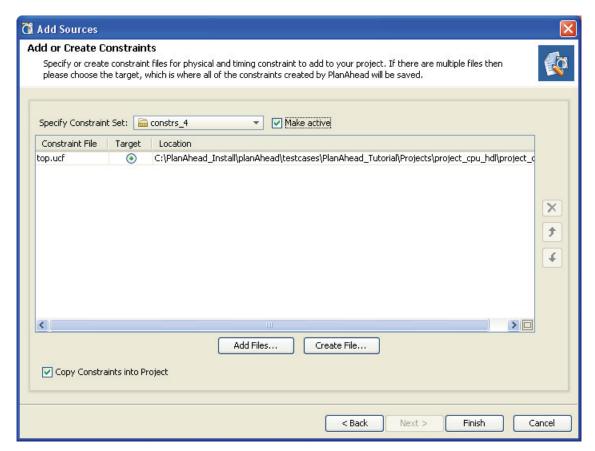

- Add Sources: Invokes the Add Sources dialog box. Refer to Managing Project Sources, page 52.

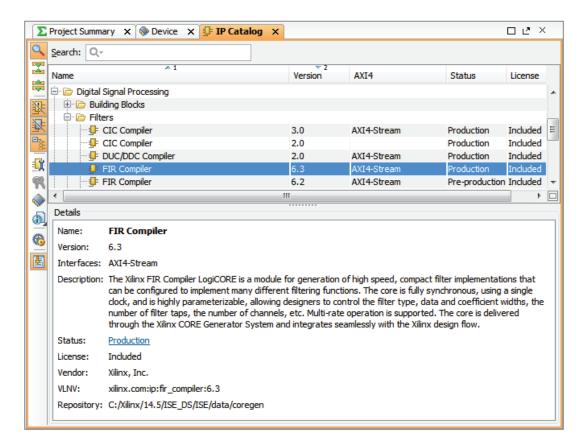

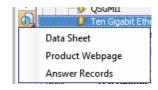

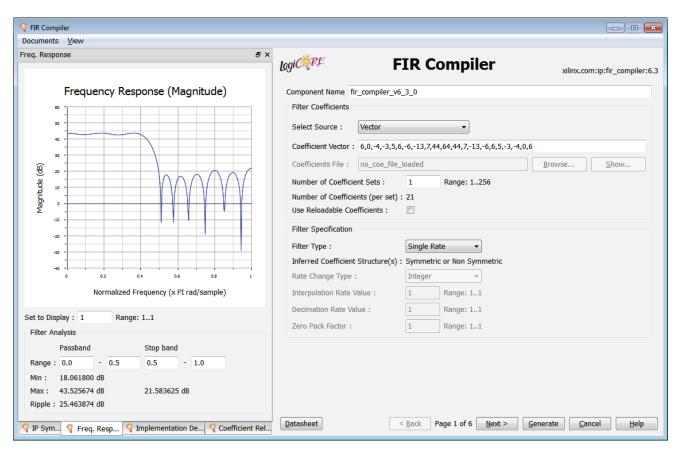

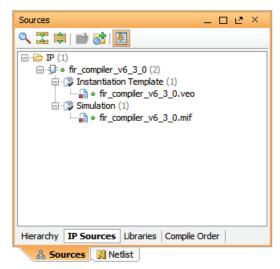

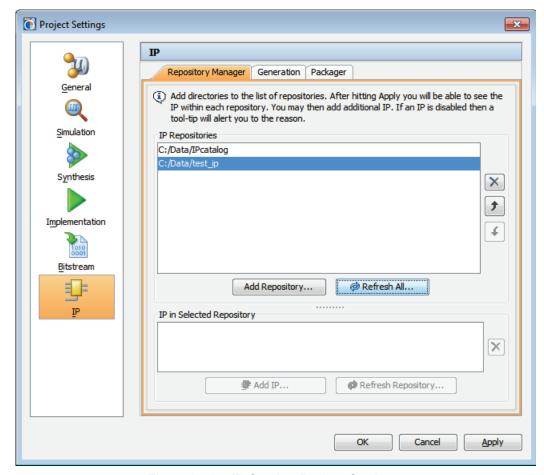

- IP Catalog: Opens the IP Catalog view. Refer to Managing IP Cores, page 66.

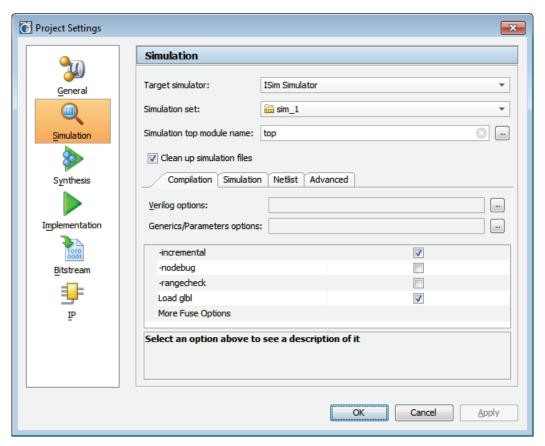

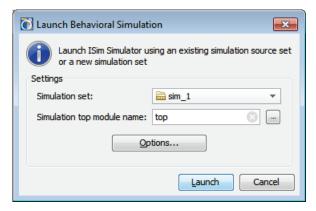

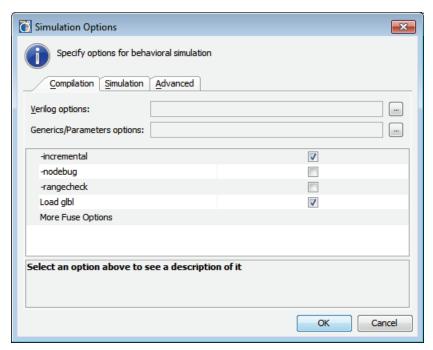

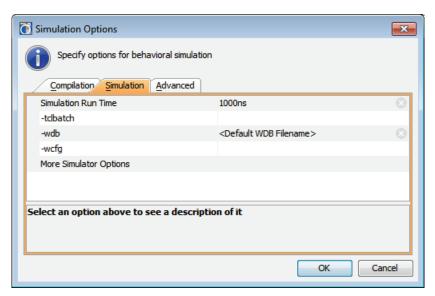

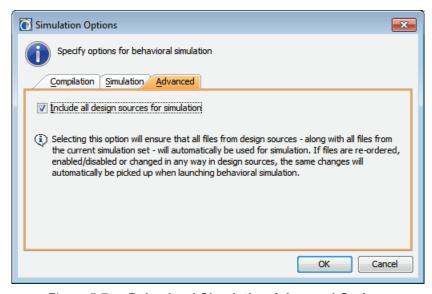

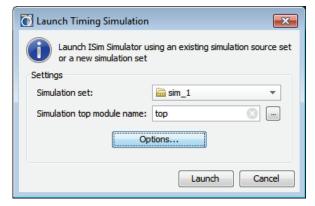

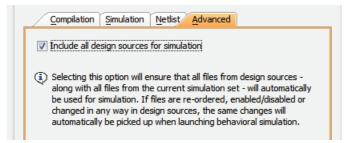

- **Run Behavioral Simulation:** Launches ISim to perform a behavioral simulation on the Elaborated Design. Refer to Performing Behavioral Simulation, page 188.

#### RTL Analysis

Open the Elaborated Design to see an un optimized view of the RTL, which is useful for understanding how the tools are interpreting the HDL. The RTL Analysis menu of the Flow Navigator provides the following commands to elaborate and analyze RTL source files:

- RTL Analysis: Click the arrow icon to expand and collapse the menu of RTL Analysis commands.

- Elaborated Design/Open Elaborated Design: The state of this command depends on whether an Elaborated Design is open or not.

- Elaborated Design: Make an open Elaborated Design the active design.

- Open Elaborated Design: If an Elaborated Design is not open, elaborate the RTL source files according to the current top module, with the associated design constraints, and create and open a schematic view. Refer to Elaborating and Analyzing the RTL Source Files, page 184.

- **Report DRC:** Run RTL-based design rule checks on the active Elaborated Design, as explained in Running RTL DRCs, page 195.

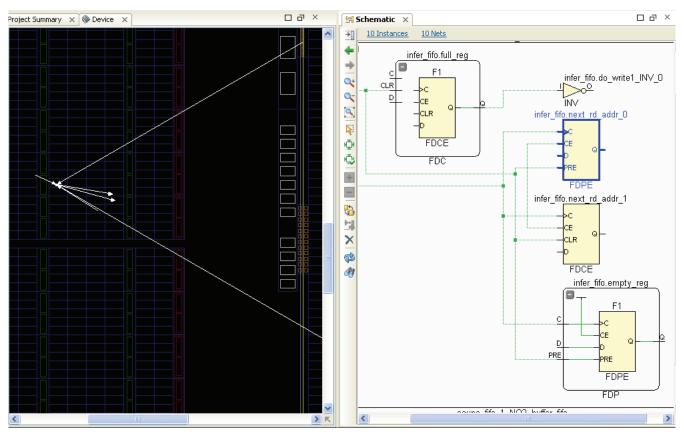

- Schematic: Create and open a schematic view of the current top module of the Elaborated Design. See Using the Schematic View, page 146.

#### Synthesis

Open the Synthesized Design to analyze the design for clock and pin-planning, floorplanning, and timing constraint creation. The Synthesis menu of the Flow Navigator provides the following commands to manage and analyze Synthesized Designs:

- Synthesis: Click the arrow icon to expand and collapse the menu of Synthesis commands.

- **Synthesis Settings:** Open the Project Settings dialog, to modify the Synthesis Settings. See Synthesis Settings, page 92 for more information.

- Run Synthesis: Launch the active synthesis run. Refer to Launching a Synthesis Run, page 204.

- **Synthesized Design/Open Synthesized Design:** The state of this command depends on whether a Synthesized Design is open or not.

- Synthesized Design: Switch the tool focus to a currently open Synthesized Design.

- Open Synthesized Design: If a Synthesized Design is not open, the tool reads the synthesized netlist, maps it to the target part, and applies the specified constraints file. Refer to Using the Synthesized Design Environment, page 209.

- Edit Timing Constraints: Open the Timing Constraints view to display, edit, and create timing constraints for the Synthesized Design. See Defining Timing Constraints, page 219 for more information.

- **Report Timing:** Report timing analysis of the Synthesized Design to ensure that paths are covered by needed constraints. See Running Timing Analysis, page 222.

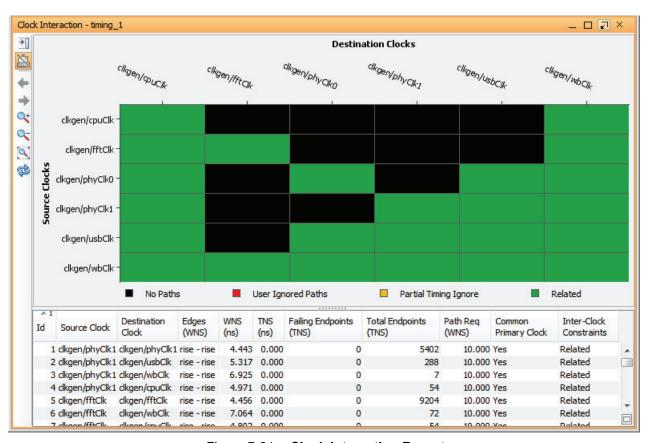

- Report Clock Interaction: The Clock Interaction Report offers information on clock interactions and signals that cross clock domains. See Analyzing Clock Interactions, page 233.

- **Report DRC:** Run design rule checks on the current Synthesized Design, as explained in Running the Design Rule Checker (DRC), page 242.

- **Report Noise:** Run SSO/SSN analysis as appropriate for the target part. Refer to Using Noise Analysis Predictors, page 278 for more information.

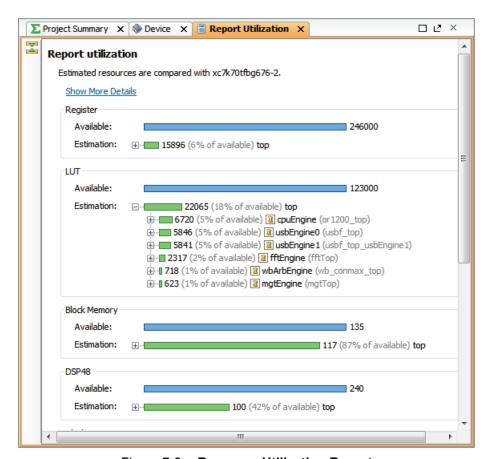

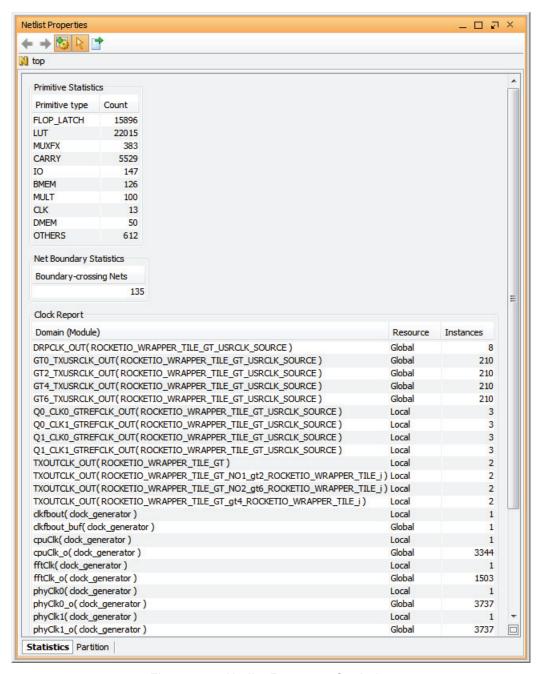

- **Report Utilization:** Report the utilization statistics for the Synthesized Design in the context of the target part. Refer to Viewing and Reporting Resource Statistics, page 211 for more information.

- **Schematic**: Create and open a schematic view of the current top module of the Synthesized Design. See Using the Schematic View, page 146.

#### Implementation

After Synthesis has completed, you can run the implementation tools in the Flow Navigator to place and route the design. The Implementation menu of the Flow Navigator provides the following commands to manage and analyze Implemented Designs:

- Implementation: Click the arrow icon to expand and collapse the menu of Implementation commands.

- **Implementation Settings:** Open the Project Settings dialog, to modify the Implementation Settings. See Implementation Settings, page 93 for more information.

- **Run Implementation:** Launch the active implementation run. If you have not yet run synthesis, you can still use Run Implementation and the tool completes the parent synthesis run as a prerequisite to

- 🙀 XPower Analyzer FPGA Editor Run Timing Simulation the active implementation run. See Chapter 9, Implementing the Design, for more information.

Implementation Settings

Run Implementation

Run TRCE

Report DRC

Report Noise

Report Utilization

By Open Implemented Design 🔼 Edit Timing Constraints

📰 Report Clock Interaction

Implementation

- Implemented Design/Open Implemented Design: The state of this command depends on whether an Implemented Design is open or not.

- **Implemented Design:** Switch the tool focus to a currently open Implemented Design.

- Open Implemented Design: If an Implemented Design is not open, the tool reads the synthesized netlist, processes the design constraints, reads the placement and routing results, and loads the timing results to open the Implemented Design in memory. Refer to Opening the Implemented Design, page 335.

- **Edit Timing Constraints:** Open the Timing Constraints view to display, edit, and create timing constraints for the Implemented Design. See Defining Timing Constraints, page 219 for more information.

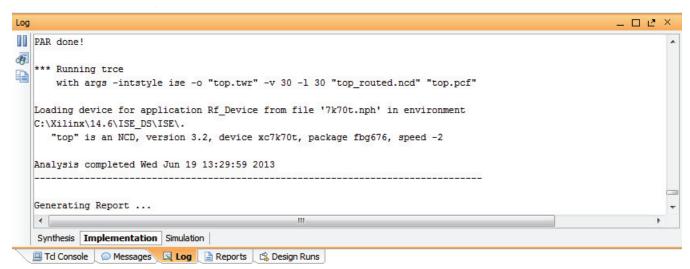

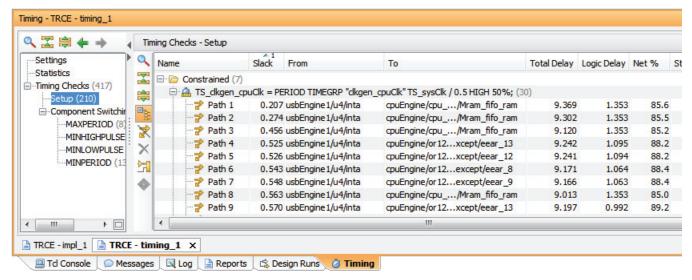

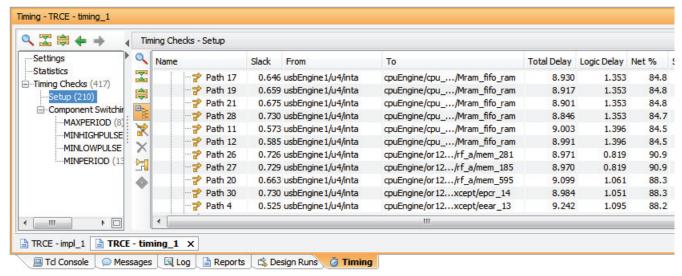

- Run TRCE: The TRCE software verifies that the design meets timing constraints, and generates a report file that lists compliance of the design against the input constraints. Refer to Analyzing Timing Results, page 338.

www.xilinx.com

- **Report Clock Interaction:** The Clock Interaction Report offers information on clock interactions and signals that cross clock domains. See Analyzing Clock Interactions, page 233.

- **Report DRC:** Run design rule checks on the current Implemented Design, as explained in Running the Design Rule Checker (DRC), page 242.

- **Report Noise:** Run SSO/SSN analysis as appropriate for the target part. Refer to Using Noise Analysis Predictors, page 278 for more information.

- Report Utilization: Report the utilization statistics for the Synthesized Design in the context

of the target part. Refer to Viewing and Reporting Resource Statistics, page 211 for more

information.

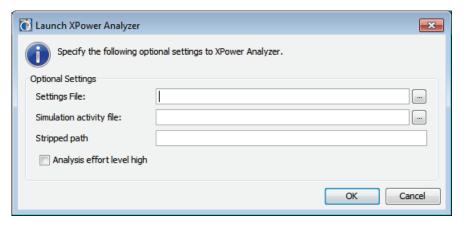

- **XPower Analyzer:** Run Power Analysis on the Implemented Design. See Analyzing Power Distribution with XPower Analyzer, page 362.

- **FPGA Editor:** Open FPGA Editor on the Implemented Design. See Launching FPGA Editor, page 363.

- **Run Timing Simulation:** Perform timing simulation on the Implemented Design. See Performing Timing Simulation, page 354.

#### Program and Debug

After Implementation has completed, you can generate bitstream files and launch the debugging and programming tools. The Program and Debug menu in the Flow Navigator provides the following commands:

Program and Debug: Click the arrow icon to expand and collapse the menu of commands under the Program and Debug heading.

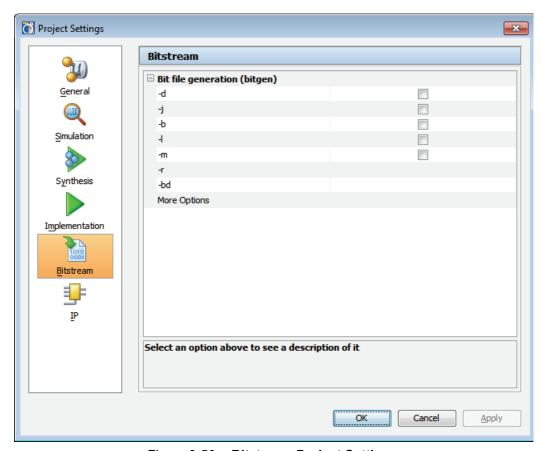

- **Bitstream Settings**: Open the Project Settings dialog, to modify the Bitstream Settings. See Bitstream Settings, page 94 for more information.

- **Generate Bitstream**: Run the BitGen command with the options specified by the Bitstream Settings dialog box.

- Launch ChipScope Analyzer: Use for launching the ChipScope Pro Analyzer product on Implemented Designs that have implemented ChipScope ILA cores. See Launching ChipScope Pro Analyzer, page 375 for more information.

- Launch iMPACT: Launch iMPACT on the Implemented Design. See Launching iMPACT, page 375 for more information.

The ChipScope Pro Analyzer and iMPACT require a BIT file, and are available only after you run the **Generate Bitstream** command. Refer to Chapter 12, Programming and Debugging the Design, for more information.

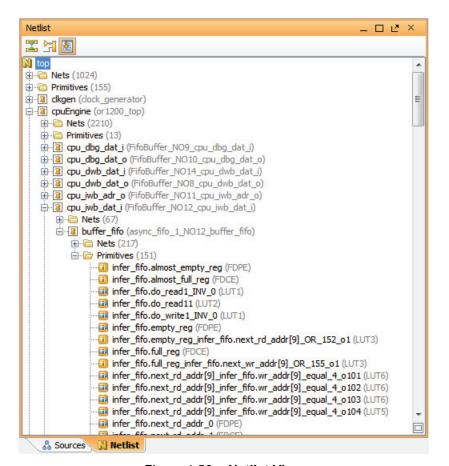

#### **Working with Designs**

The PlanAhead tool lets you open designs at various stages of the design process. A design is defined as a netlist (elaborated RTL or synthesized), a constraint set, and a target device. The PlanAhead tool loads the design into memory for analysis, constraint definition, or ChipScope debug core insertion.

The Flow Navigator has buttons for Elaborated Design, Synthesized Design, and Implemented Design. The Implemented Design loads the specific design data used to launch the run. You can open the Elaborated and Synthesized Designs with different target devices and/or constraint sets allowing experimentation and constraints version control.

You can analyze the design at various stages of completion, including elaborated RTL, synthesized netlist, or implemented results. You can make design changes by editing constraints such as timing or floorplanning and placing logic at any phase by opening the appropriate design.

Constraint change management is made possible by the ability to create and manage multiple constraints files. The available levels of design abstraction that you can open in the PlanAhead tool environment are:

- Elaborated Design: Elaborated RTL source files, constraint set, and target device.

- Synthesized Design: Synthesized netlist, constraints, and target device.

- Implemented Design: Synthesized netlist, constraints, and results from any implemented run.

For all design views, the default view layout in the GUI includes a graphical view of the design, such as the Schematic or Device view, the Netlist view, the Properties view, and the Messages and Reports views at the bottom of the workspace. Select a different view layout in the menu toolbar to toggle between different arrangements of the various views. See Using View Layouts, page 102.

#### Opening an Elaborated Design

An elaborated RTL design consists of multiple RTL source files, for synthesis and simulation, can include synthesized netlists for modules and IP cores to be used in the design, constraints files to hold timing and physical constraints, and a Xilinx part which is the target device for the design.

When you click **Open Elaborated Design** in the Flow Navigator, the PlanAhead tool automatically elaborates the RTL source files and loads the elaborated netlist into memory along with the active constraint set and the target part. Elaboration messages display in the Messages view.

To open a Elaborated Design, select either:

- The **Open Elaborated Design** command in the RTL Analysis menu of the Flow Navigator to load the elaborated netlist, the active constraint set, and the target device into memory.

- Flow > Open Elaborated Design from the main menu.

- New Elaborated Design accessed from the RTL Analysis popup menu in the Flow Navigator.

- Flow > New Elaborated Design from the main menu.

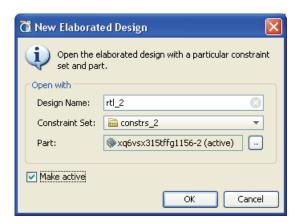

You can specify the name for a new Elaborated Design, the constraint set to apply, and the target part to load into the design, as shown in Figure 2-4, page 25.

**Note:** If you select a constraint set that is not the active constraint set, you can also choose to make it active. See Managing Constraints, page 53 for more information.

Figure 2-4: New Elaborated Design

When you click OK, the RTL design is elaborated to create an expanded netlist for the design. This is not a fully synthesized netlist, but permits some analysis of the design beyond what is possible from the RTL files.

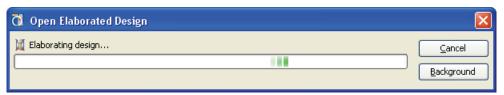

#### Moving Processes to the Background

As the PlanAhead tool spawns the process to perform elaboration, reading the various design files and constraint files, the Open Elaborated Design dialog box opens, to let you put the elaboration process into the background, as shown in Figure 2-5.

When you put a process into the background, it releases the PlanAhead tool to perform certain other functions, like viewing reports, or opening design files, while it completes the background task. You can make use of this time to review reports for instance. However, the Tcl Console is blocked, and you will not be able to use Tcl commands, or perform tasks that require Tcl commands, such as switching to another open design.

Figure 2-5: Open Elaborated Design - Background Process

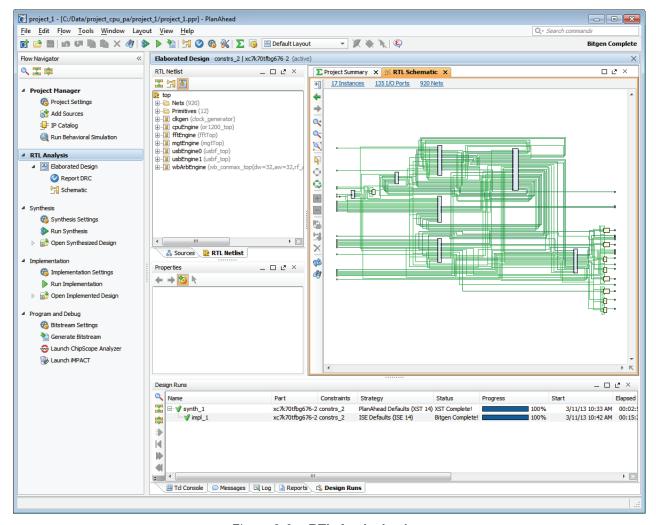

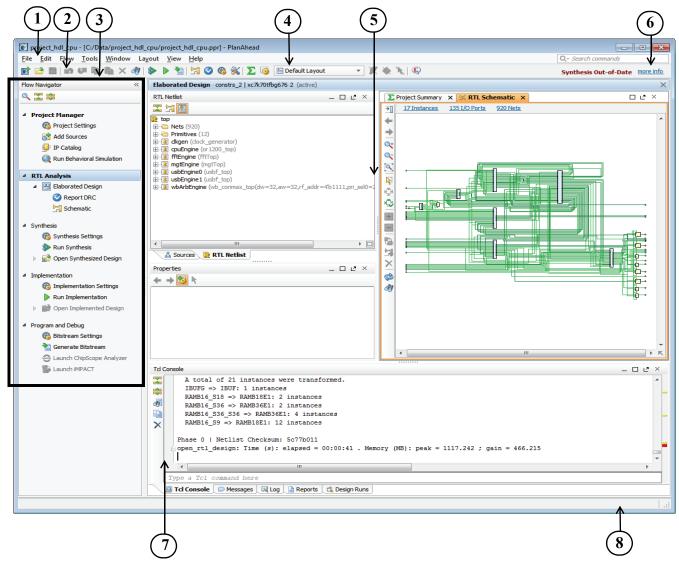

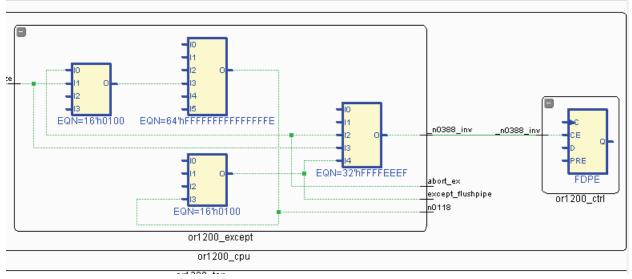

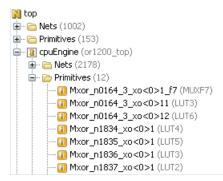

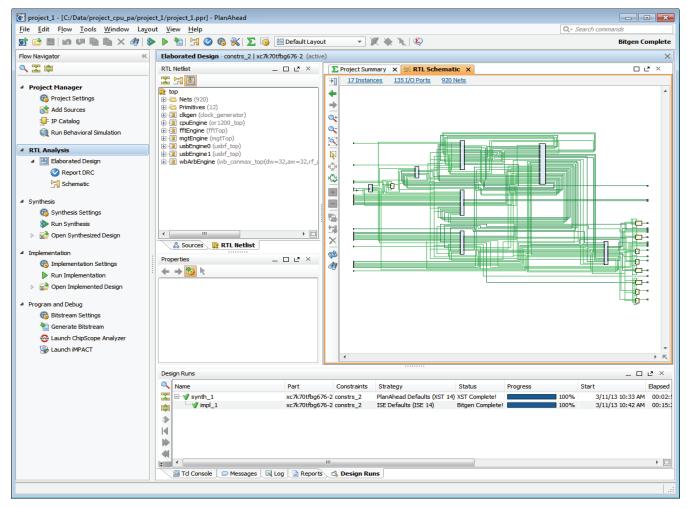

The Elaborated Design view is opened with the default view layout, including the RTL Netlist view and Schematic view of the top-level schematic, as shown below.

The RTL Netlist view displays the elaborated logic hierarchy. See Chapter 5, Elaborated RTL Design for more information on analyzing the RTL logic design.

Figure 2-6: RTL Analysis view

#### Setting the Active Run

When opening a Synthesized design, or an Implemented Design, the PlanAhead tool default is to apply the netlist and the placement and routing data from the currently active run. The Flow Navigator menu is sensitive to the active run, with commands like Open Synthesized Design and Open Implemented Design dependant upon whether the active run has completed synthesis or implementation. The Project Summary, Log view, and Messages view also display information about the active run.

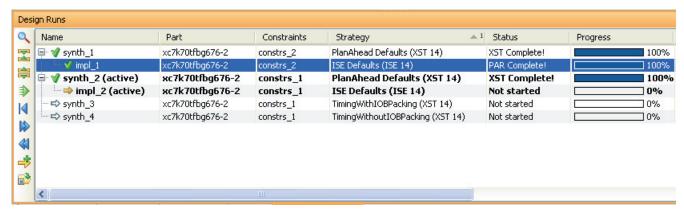

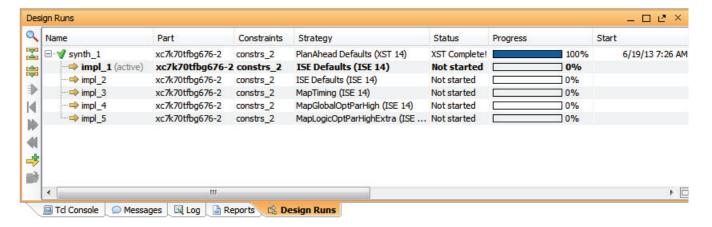

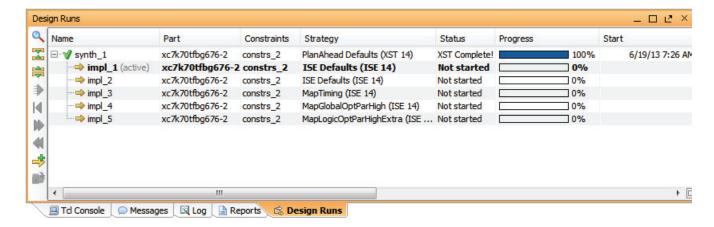

If multiple synthesis or implementation runs exist, the PlanAhead tool applies the netlist and design information from the currently *active run*. The active run displays in bold text in the Design Runs view, as shown in Figure 2-7, page 28.

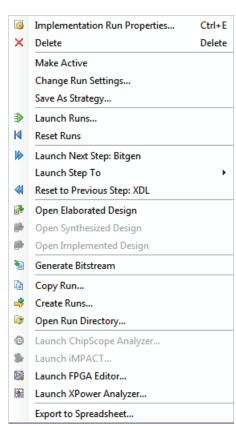

To change the active run, select the **Synthesis Run** or **Implementation Run** in the Design Runs view, then use the **Make active** command in the popup menu. The PlanAhead tool then uses the netlist or placement and routing data of the new active run when opening designs or launching runs. See Using the Design Runs View, page 165 for more information.

Figure 2-7: Design Runs view

For more information on creating and managing multiple runs, see Defining Implementation Runs, page 287.

#### Opening a Synthesized Design

The PlanAhead tool creates a Synthesized Design using combinations of a synthesized netlist, physical and timing constraints, and a target part.

When it is opened, the different elements of the Synthesized Design are loaded into memory, where you can analyze them and modify design elements as needed to complete the design. You can save the Synthesized Design, updating the constraints file, or reload the design without saving to restore the original design.

To open a Synthesized Design, select either:

- Double-click on the run name in the Design Runs view.

- Open Synthesized Design command in the Synthesis menu of the Flow Navigator.

- Flow > Open Synthesized Design command from the main menu.

- **New Synthesized Design** from the popup menu of the Synthesis command of the Flow Navigator.

- Flow > New Synthesized Design command from the main menu.

You can open the synthesized netlist with the active constraint set, and the target device, or specify an alternative constraint set and target device to open the Synthesized Design in memory. As shown in Figure 2-8, page 29, you can enter the following to define a new Synthesized Design:

- **Design Name:** Enter a name to display in the view banner. The design is stored in memory during the session only.

- Constraint Set: Select an existing constraint set to be opened against the netlist.

- Part: Select a target part.

Figure 2-8: New Synthesized Design

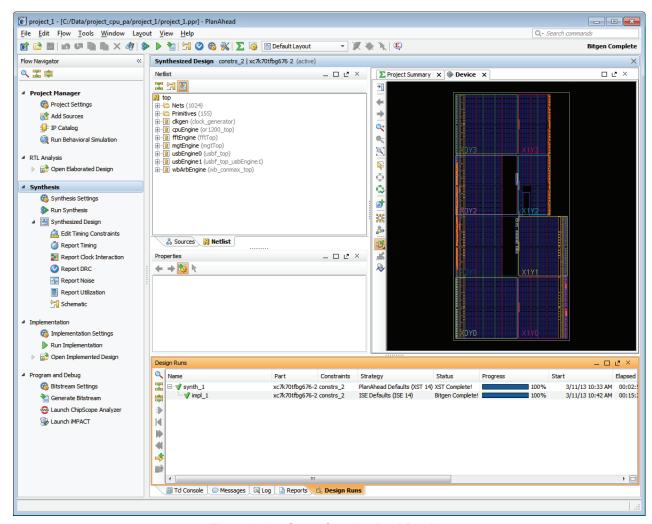

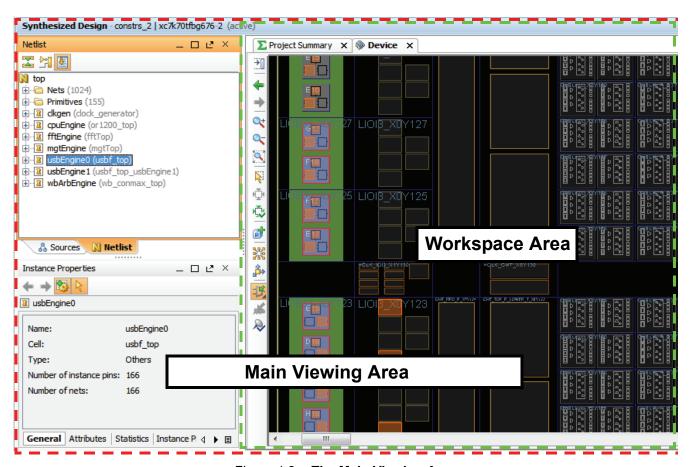

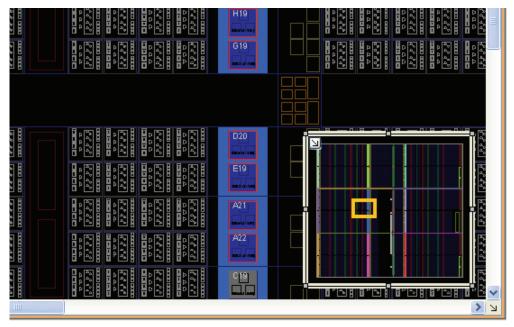

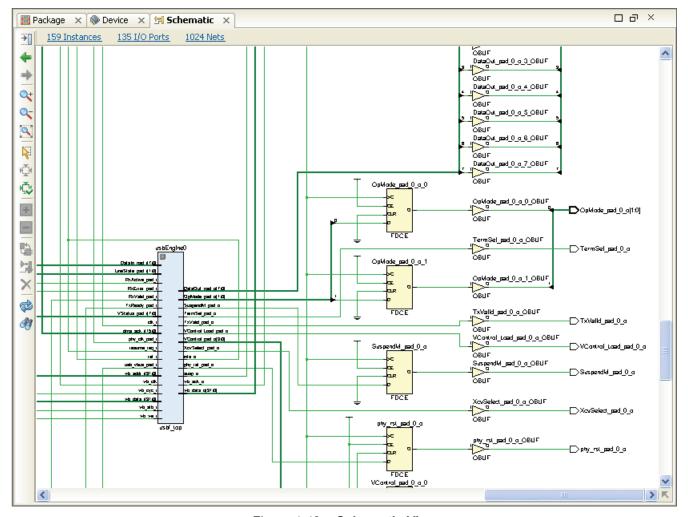

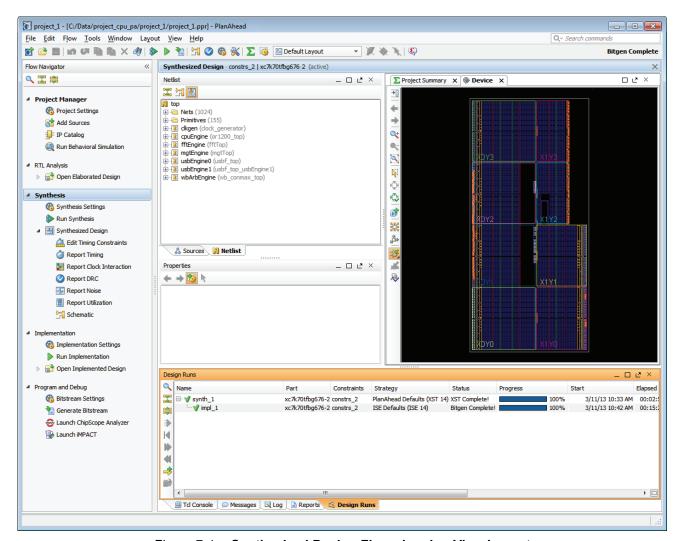

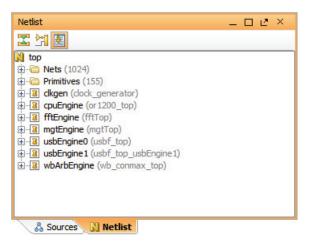

Figure 2-9 shows the default view layout of the open Synthesized Design.

Figure 2-9: Open Synthesized Design

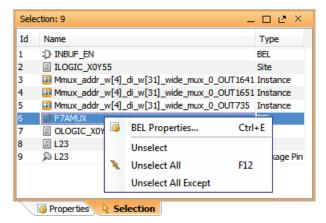

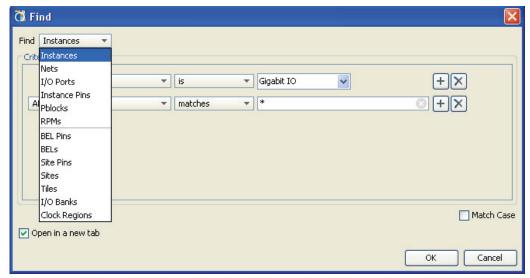

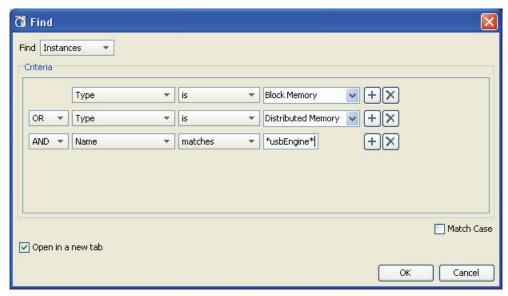

#### Moving Processes to the Background

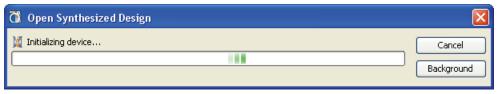

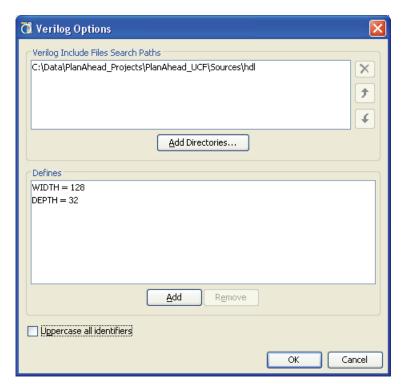

As the PlanAhead tool spawns the process to open the Synthesized or Implemented Designs, reading design files and constraint files, the Open Synthesized Design dialog box or Open Implemented Design dialog box lets you put the process into the background, as shown in Figure 2-10.

When you put a process into the background, it releases the PlanAhead tool to perform certain other functions, like viewing reports, or opening design files, while it completes the background task. You can make use of this time to review previous runs for instance, or examine reports. However, the Tcl Console is blocked, and you will not be able to use Tcl commands, or perform tasks that require Tcl commands, such as switching to another open design.

Figure 2-10: Open Synthesized Design - Background Process

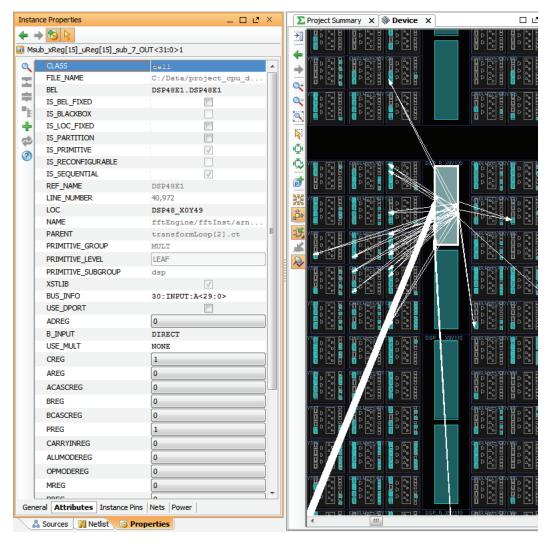

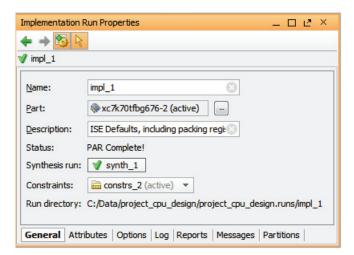

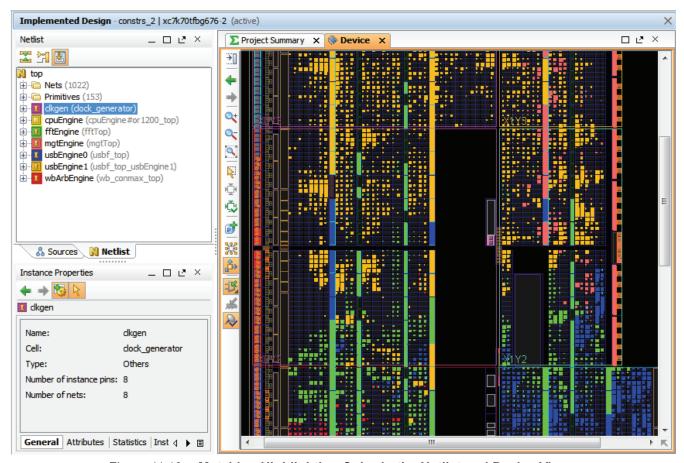

#### Opening an Implemented Design

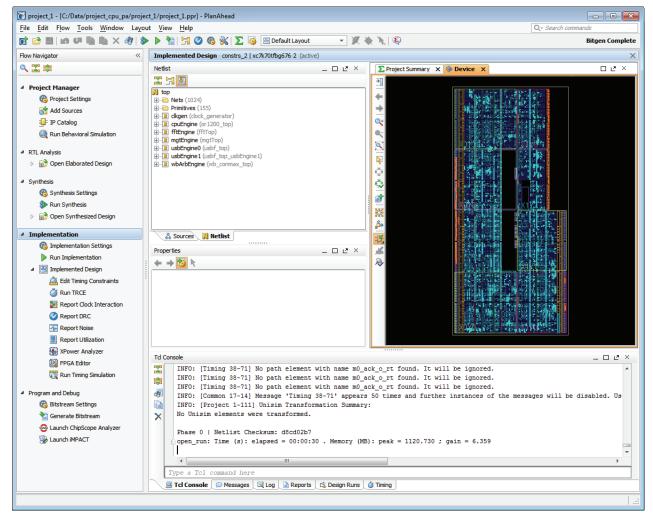

An Implemented Design consists of a synthesized netlist, physical and timing constraints, the target XIIinx part, and placement and routing data from a completed implementation run. Because the PlanAhead tool allows for multiple implementation runs, you can select any completed implementation run to open in the Implemented Design.

The Implemented Design imports the netlist, constraints, placement, and timing results from the implementation run directory. The PlanAhead tool loads the Implemented Design into memory where you can analyze it and make any needed design changes.

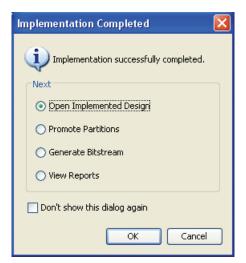

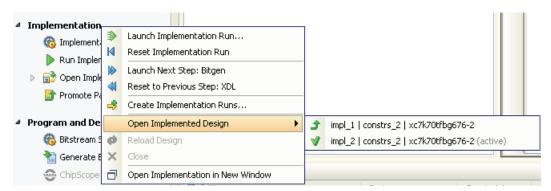

To open an Implemented Design, select one of the following methods:

- Double-click on the run name in the Design Runs view.

- Flow > Open Implemented Design in the main menu.

- Open Implemented Design from the Implementation menu in the Flow Navigator.

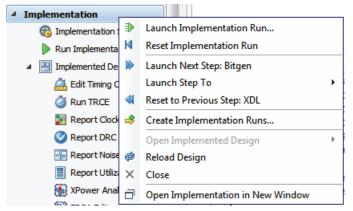

Since the Flow Navigator reflects the state of the active run, the Open Implemented Design command may be disabled, or greyed out, if the active run is not implemented. In this case, the Implementation popup menu in the Flow Navigator will allow you to open an Implemented Design from any completed implementation runs.

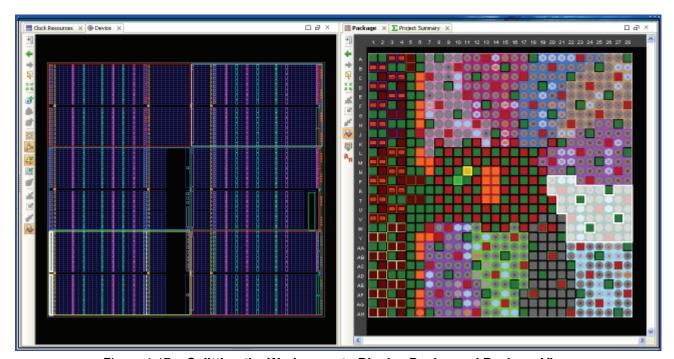

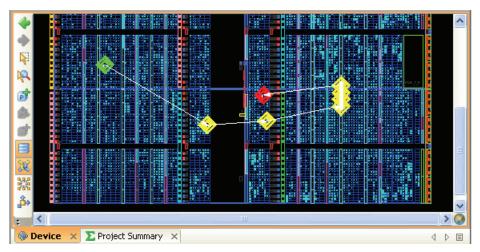

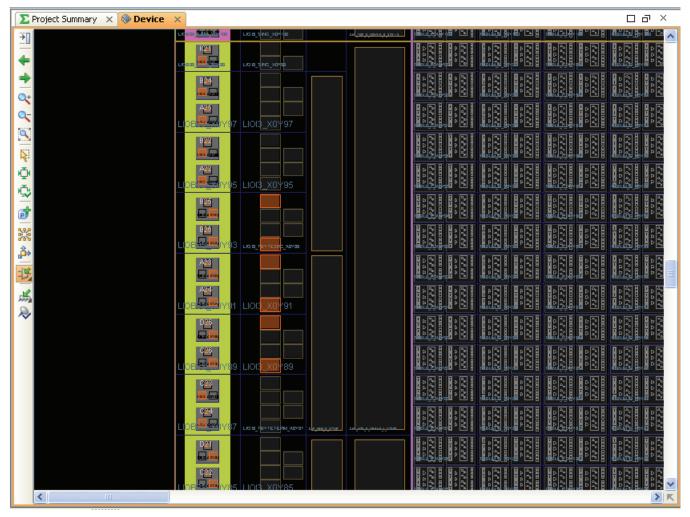

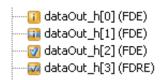

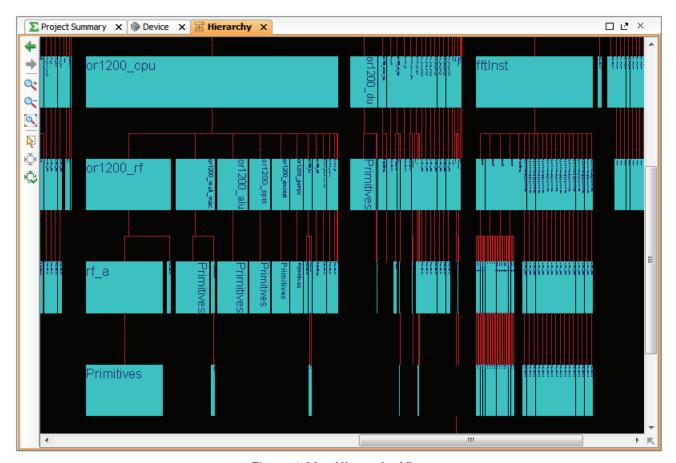

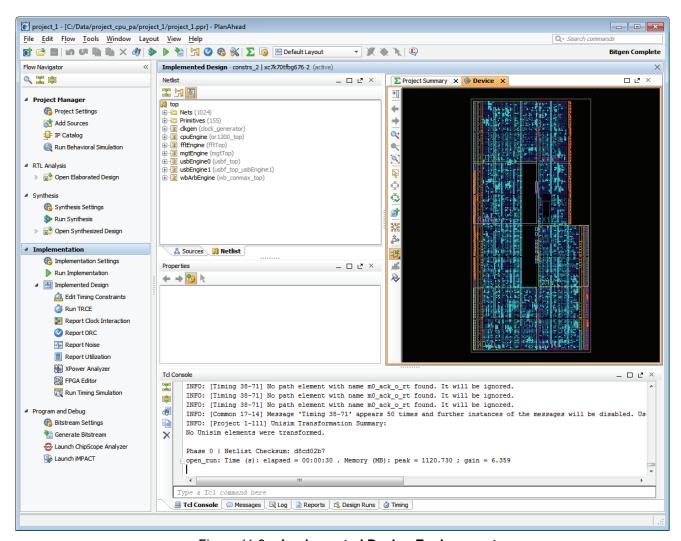

The Implemented Design default view opens. Typically, you do placement and timing analysis and floorplanning in this view. Figure 2-11, page 31 shows the default layout view of an open Implemented Design.

Figure 2-11: Open Implemented Design

#### Managing Open Designs

As you open designs and the PlanAhead tool loads the design into memory, the associated menu in the Flow Navigator is highlighted. This provides you with a visual reference of the current design. Figure 2-12, page 32 shows the highlighted RTL Analysis menu. This indicates that an Elaborated Design is both opened and active in the current session.

You can open multiple Elaborated Designs, Synthesized Designs, and Implemented Designs simultaneously to display the results of different design options and different runs.

When multiple designs are open, the Flow Navigator provides multiple indications of the open designs. In Figure 2-12 the Synthesized Design command under the Synthesis menu reflects the fact that a Synthesized Design is open, but is not the active design. Selecting the **Synthesized Design** command will make the open design the active design, and will move the highlighting from RTL Analysis to Synthesis. The grey Open Implemented Design command under the Implementation menu indicates that implementation has not been completed, and there is no available Implemented Design for the active implementation run.

Figure 2-12: Open Designs in Flow Navigator

The Flow Navigator also supports a popup menu accessed from the right mouse button (RMB). Click the RMB over the Project Manager, RTL Analysis, Synthesis, or Implementation commands in the Flow Navigator, and a popup menu is displayed. Figure 2-12 shows the Synthesis popup menu.

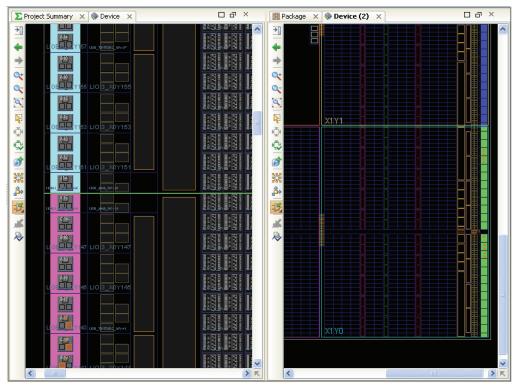

The **Open Netlist in New Window** lets you open a new PlanAhead window with the Synthesized Design, while maintaining the current window with the currently open design. You can use this command to view the Elaborated Design in one window and open the Synthesized Design or Implemented Design in a second window. You can zoom and pan, and select different elements of the design, analyzing and developing both design views.

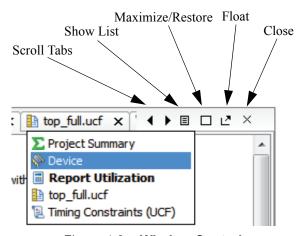

#### Using the Design View Banner

The Design View banner reflects the content of the current design, displaying the constraint set, and target part, as well as the synthesis or implementation run as appropriate. Figure 2-13, page 32 shows the Design View banners for each of the different design types.

Figure 2-13: Design View Banners

If multiple designs are open, tabs display in the Design View banner to let you toggle between the open designs, as shown in Figure 2-14.

Figure 2-14: Multiple Open Design Tabs

#### **Updating and Reloading Designs**

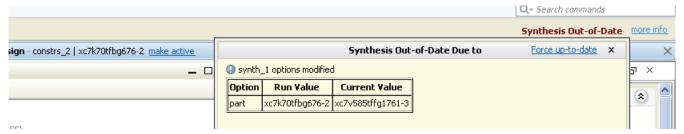

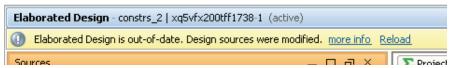

In the course of any design process, source files or constraints often require modification. The PlanAhead tool manages the dependencies of these files, and indicates when the design data in the current design is out-of-date. Changing project settings, such as the target part or active constraint set, can also make a design out-of-date.

When the target part or constraint set of the open design are different from the constraint set or target part of the active synthesis or implementation runs, the Design View banner displays the **make** active link, as shown in Figure 2-14. Clicking on the **make active** link sets the constraint set and target part of the current design as the active constraint set and target part for the current project, and the active synthesis and implementation runs.

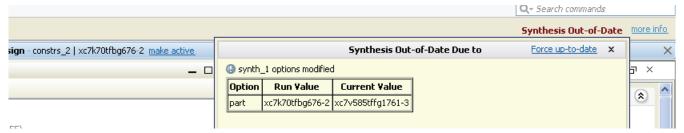

As source files, netlists, or implementation results are updated, an "out-of-date" message is displayed at the right side of the Design View banner of an open Synthesized Design or Implemented Design to indicate that the run is out of date, as shown in Figure 2-15. Click the **more info** link to display what aspects of the design are out of date.

Figure 2-15: Design Out-of-Date and Reload Banner

There are three actions you can take to resolve an out-of-date design:

• **Force up-to-date**: Select the **Force up-to-date** link in the "Out-of-Date Due to" window that is opened when you click **more info** as shown in Figure 2-15.

Force up-to-date will reset the NEEDS\_REFRESH property on the active synthesis or implementation runs as needed to force them into an up-to-date state. The Tcl command for this is shown in the following sample code:

```

set property needs refresh false [get runs synth 2]

```

**Note:** Use this command to force designs up-to-date when a minor design change was made, and you do not want to refresh the design because of it.

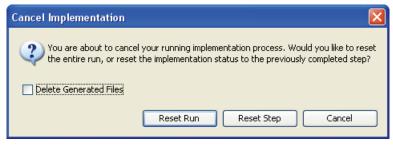

- **Reset and Rerun:** Select the **Reset Runs** command from the Design Runs view, or from the popup menu of the Synthesis or Implementation commands in the Flow Navigator. This will reset the run to allow it to be rerun and updated with the current project settings.

- You can also use the **Launch Runs** command directly. The tool will warn you that the run needs to be reset first, and prompt you to confirm before proceeding.

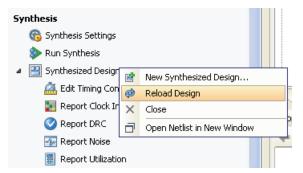

- **Reload the Design**: Use the **Reload Design** command, in the Flow Navigator popup menu as shown in Figure 2-16, to revert any changes and reload the original netlist, constraints, and target part of the design.

This Reload Design command will refresh the in-memory view of the current design, eliminating any changes that you made to the design data that have not been saved.

Figure 2-16: Reload Design

#### Saving Designs

To save any changes you have made to your design data, click File > Save Constraints.

The **Save Constraints** command saves any changes to the constraint files, design partitions, ChipScope cores and configuration added to the Synthesized Design, and project settings.

When an Implemented Design is open, **Save Constraints** saves any changed constraints to the constraint file associated with the implementation run, and used during implementation, rather than saving to the currently active constraint file. This ensures that the changes to the Implemented Design are saved with the proper constraint file for the implementation run.

However, this can cause unintended changes to the constraint files used for a specific implementation run, and may not be the intended result. The PlanAhead tool warns of this situation, and lets you choose the constraint file to target changes to before writing changes to disk.

You can also save changes to the design in a new constraints file, to preserve your original design, while still saving any changes. Use the **File > Save Constraints As** command to create a new constraint file, while preserving the original design.

#### Closing Designs

You can close designs to reduce the number of designs in memory and to prevent multiple locations where sources could be edited. In some cases, you are prompted to close a design prior to changing to another design representation. In some cases, such as for a Partial Reconfiguration design, you must close the design when leaving the design. You can close:

• Individual designs by clicking **Close** in the banner of the main viewing area.

All designs by selecting the Close All command from the popup menu in the Flow Navigator.

## Working with Projects

This chapter discusses working with projects, including:

- Project Types

- Creating a New Project

- Managing Projects

- Managing Project Sources

- Managing Design Source Files

- Managing Constraints

- Managing Simulation Sources

- Managing IP Cores

- Managing DSP Sources

- Managing Embedded Processor Sources

- Using the Project Summary view

- Configuring Project Settings

#### **Project Types**

You can use the PlanAhead™ application at different points in the FGPA design flow. To accommodate this, you can create the following types of projects:

- Register Transfer Level (RTL) source-based

- Synthesized netlist-based

- Implemented design results-based

- I/O pin planning projects Comma Separated Values (CSV), User Constraint File (UCF)-based

- Projects created in ISE® Project Navigator

- Partial Reconfiguration projects (with an enabled license)

These projects are differentiated by the input source types used to create the project. You can select the type of project during the Create New Project process.

With the exception of an I/O Pin Planning project, a project cannot be changed to a different project type after it has been created. The I/O Pin Planning project can be used as the foundation of an RTL-based design project, and migrated at any time.

#### RTL Source-Based Projects

You can use the PlanAhead tool to manage the entire FPGA design flow from RTL creation through bitstream generation. You can add RTL source files, EDIF netlists for blocks of the design, as well as IP generated by the CORE Generator<sup>TM</sup> tool and precompiled NGC/NGO-format IP netlists to the project.

You can elaborate and analyze the RTL to ensure proper constructs, launch, and manage various synthesis and implementation runs, and analyze the design and run results. You can also experiment with different constraints or implementation strategies.

#### Synthesized Netlist-Based Projects

You can create projects from designs that were synthesized outside of the PlanAhead tool using the Xilinx® Synthesis Technology (XST) tool or any supported third party synthesis tool. The PlanAhead tool can import EDIF and NGC/NGO-format netlists. The netlist can be all-inclusive in a single file or hierarchical in nature, consisting of multiple, module-level netlists.

You can analyze the logic netlist, launch and manage various Implementation runs, and analyze the design and run results. You can also experiment with different constraints or implementation strategies.

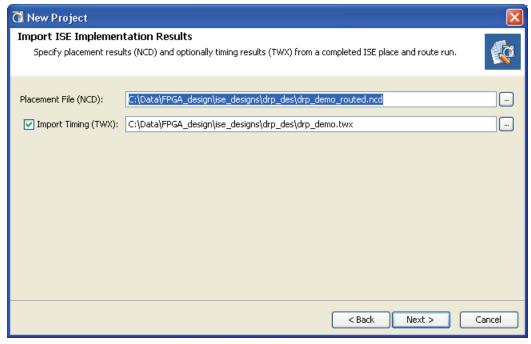

#### Implemented Design Results-Based Projects

You can create projects to allow analysis of implementation results created outside of the PlanAhead tool using the Xilinx command line tools. You can import a design netlist, implementation, and timing results to explore timing or placement related issues in the PlanAhead tool.

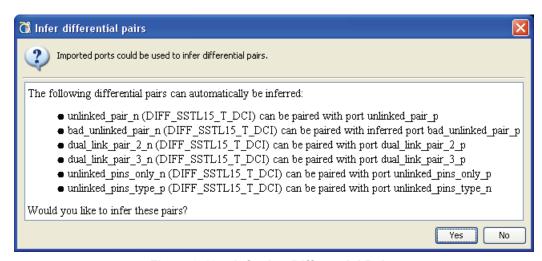

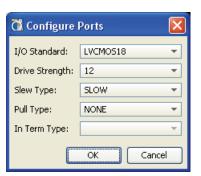

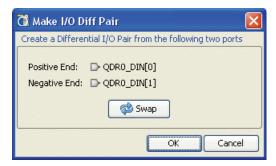

#### I/O Pin Planning Projects

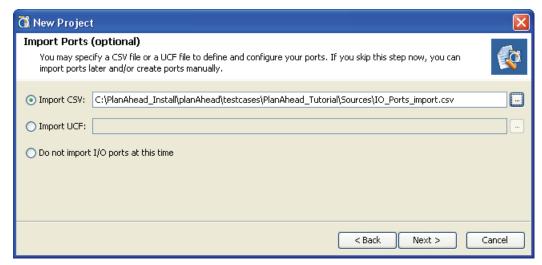

You can perform I/O pin planning early in the design cycle by creating an empty I/O Pin Planning project. You can create I/O ports within the PlanAhead tool or import them with either CSV or User-Constraint Files (UCF) input files. You can also create pin planning projects to explore the logic resources available in the different device architectures.

After I/O pin assignment, the PlanAhead tool can create CSV, UCF, and RTL output files for use later in the design flow when RTL sources or netlists are available. The output files can also be used to create schematic symbols for use in the Printed Circuit Board (PCB) design process.

An I/O Pin Planning project can be used as the foundation of an RTL-based design project. See Migrating to an RTL Design, page 275 for more information.

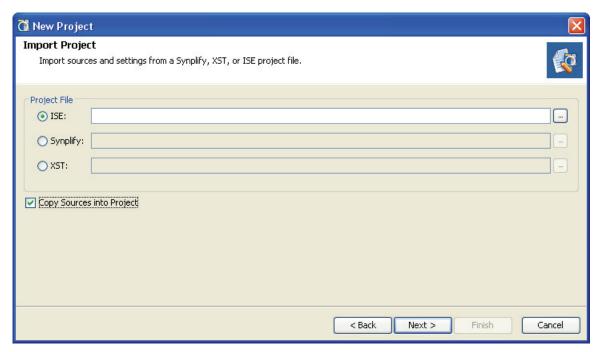

#### Externally Created Projects

You can import project data from ISE Project Navigator, from XST, or from Synopsys® Synplify® to migrate an RTL-level project into PlanAhead. The PlanAhead tool uses the various project settings from the source project when creating this new project.

**Note:** You can also launch the PlanAhead tool from within Project Navigator for performing I/O Pin Planning and Floorplanning of ISE designs. For information about using PlanAhead tools from the ISE Project Navigator environment, refer to Chapter 15, Using PlanAhead With Project Navigator.

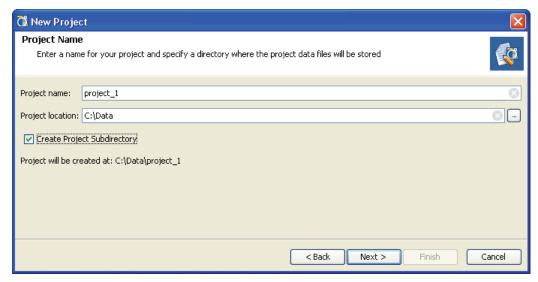

# **Creating a New Project**

The New Project wizard takes you through the individual steps to define a project name and location, add source files and constraint files to the project, and select a target device.

To create a new project:

- 1. Select one of the following:

- On the Getting Started page, click Create a New Project.

- Select File > New Project or the New Project toolbar button.

The first dialog box of the New Project wizard gives an overview of the wizard.

2. Click **Next** to continue.

The Project Name page opens, as shown in Figure 3-1.

Figure 3-1: Create Project

- 3. In the Project Name page, specify a project name and disk storage location:

- **Project name:** Enter a name to identify the project directory (for example, project 3).

- Project location: Enter a location to create the new project directory.

- Create Project Subdirectory: Use this checkbox to indicate whether the PlanAhead tool

should add a subdirectory of the same name as the project within the specified project

location.

If you enable this checkbox, which is the default, the project file (.ppr) is created at created\_location/created\_name, and all folders and data files created for the project are stored in the created\_name subdirectory.

If you disable this checkbox, the project file (.ppr) is created at project\_location, and all folders and data files created for the project are stored in that project location.

4. Click Next.

# Selecting the Project Type

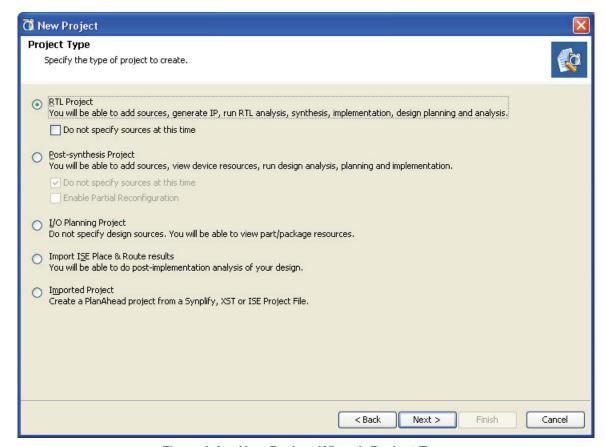

Designate the Project Type by selecting one of the options shown in Figure 3-2, page 38. This selection determines the type of source files that can be associated with the project.

Figure 3-2: New Project Wizard: Project Type

- 5. Select the design source, and click **Next**.

- 6. Depending upon the type of project you are creating, continue with the instructions in one of the following sections:

- Creating an RTL Project

- Creating a Post-synthesis Project

- Creating an I/O Planning Project

- Creating a Project with ISE Placement and Timing Results

- Importing an External Project

The next pages of the wizard guide you through adding appropriate sources to the project based on the project type you selected in the previous steps.

# Creating an RTL Project

You can specify RTL source files to create a project. This can be used for RTL code development and analysis purposes as well as synthesis and implementation. See Chapter 5, Elaborated RTL Design for more information on RTL development and analysis.

- 1. Follow the project creation steps previously described in Creating a New Project, page 37.

- 2. In the Project Type page shown in Figure 3-2, select the RTL Project option.

- a. If desired, select the **Do not specify sources at this time** checkbox, and go to Selecting a Default Part or Board, page 45. This will skip the following steps of adding sources files and constraints, and allow you to select the target part and create the project.

- 3. Click Next.

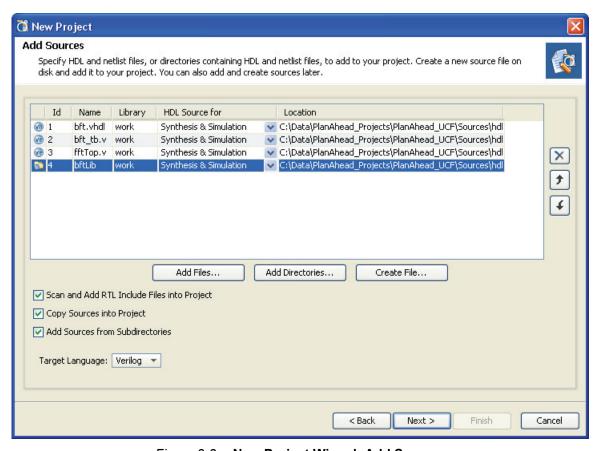

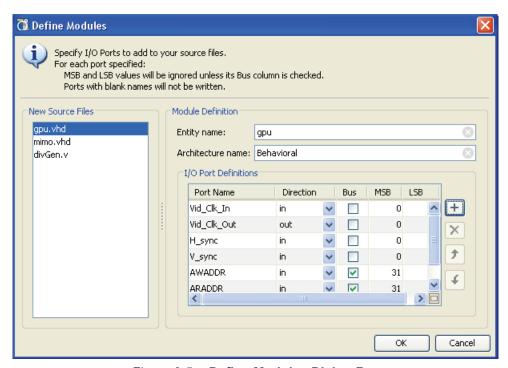

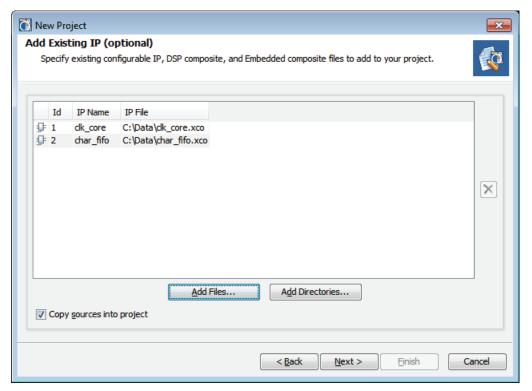

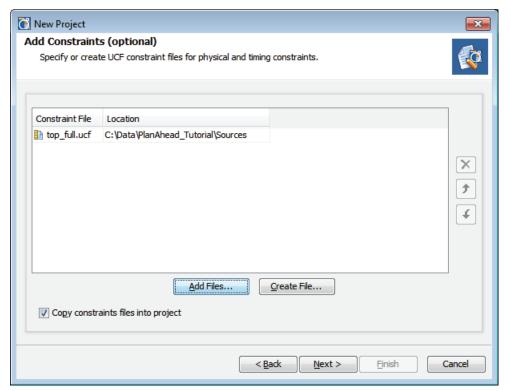

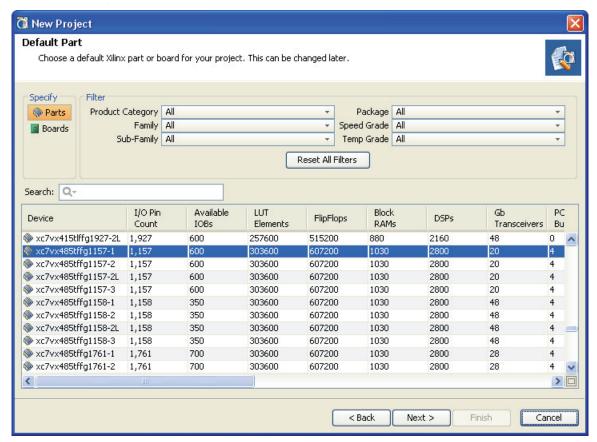

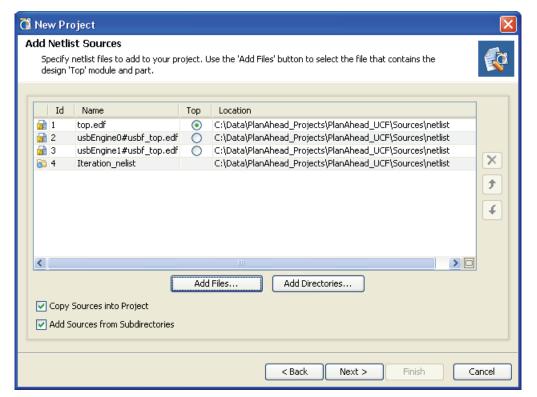

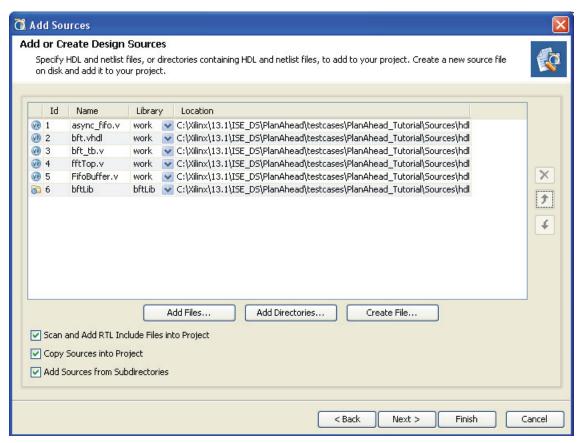

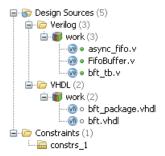

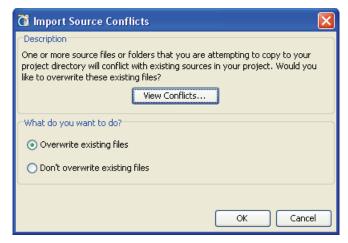

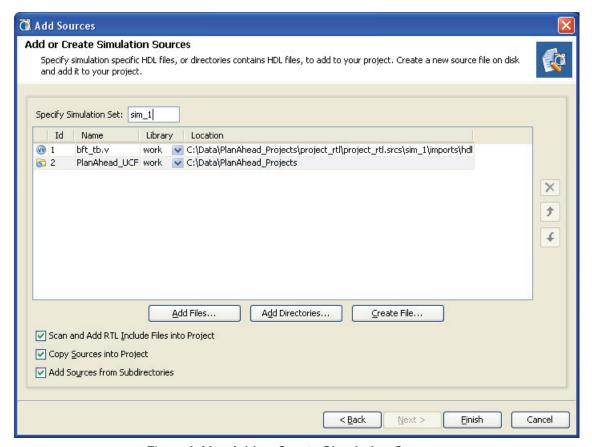

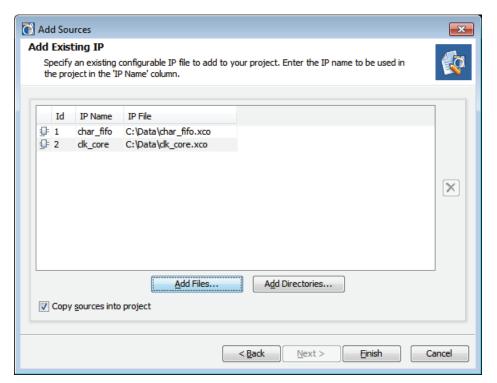

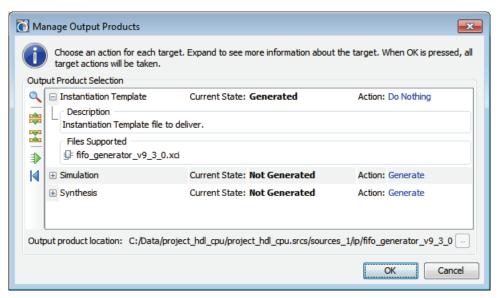

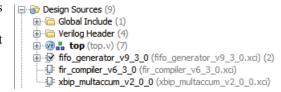

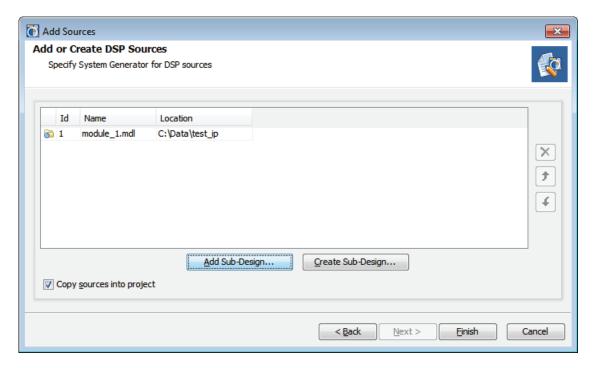

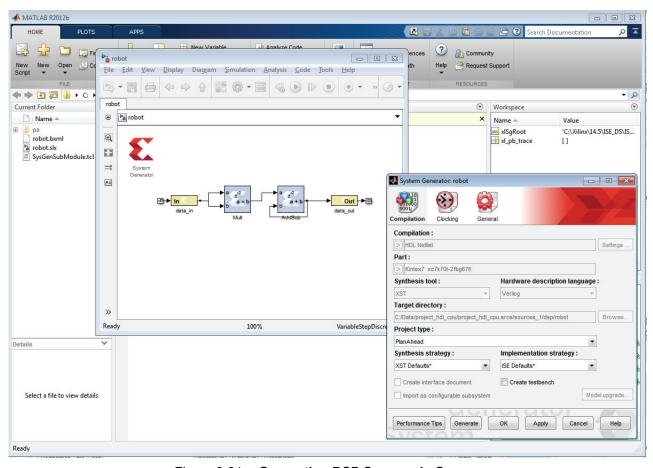

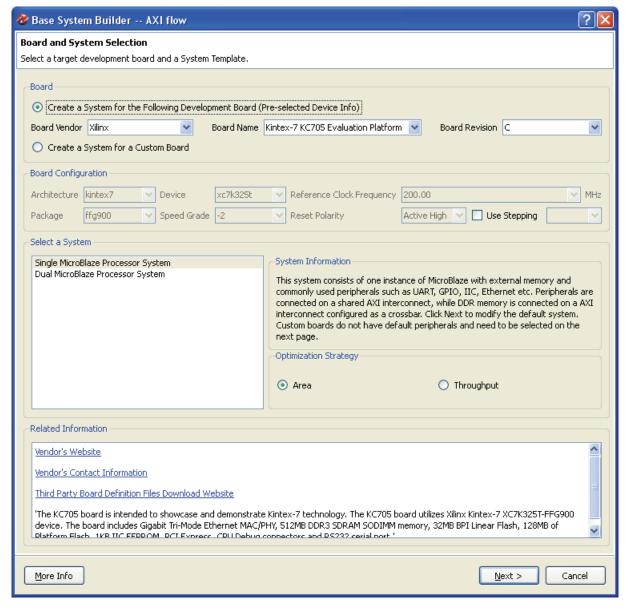

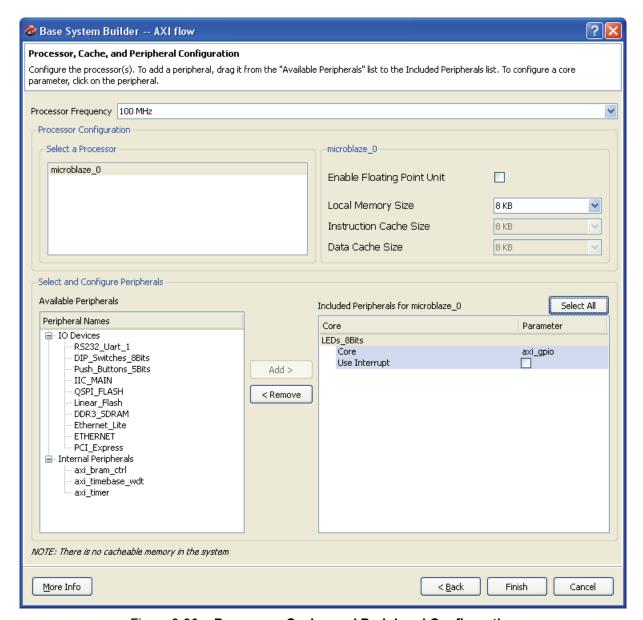

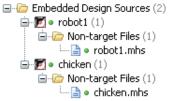

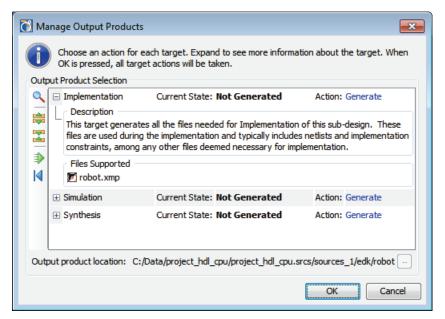

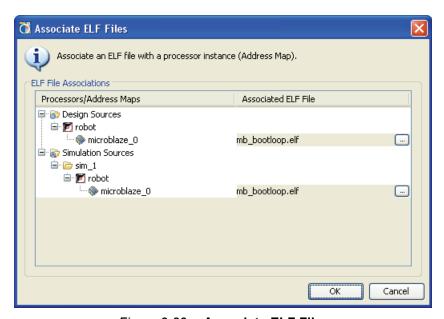

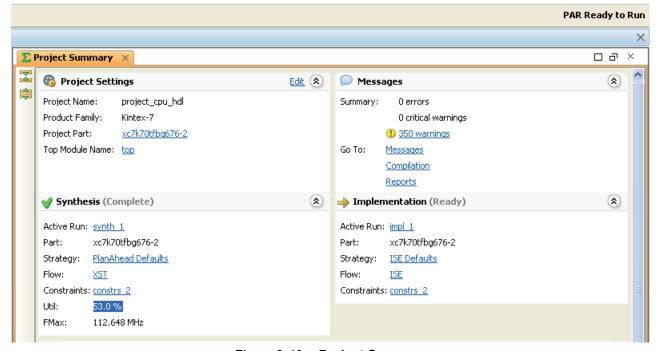

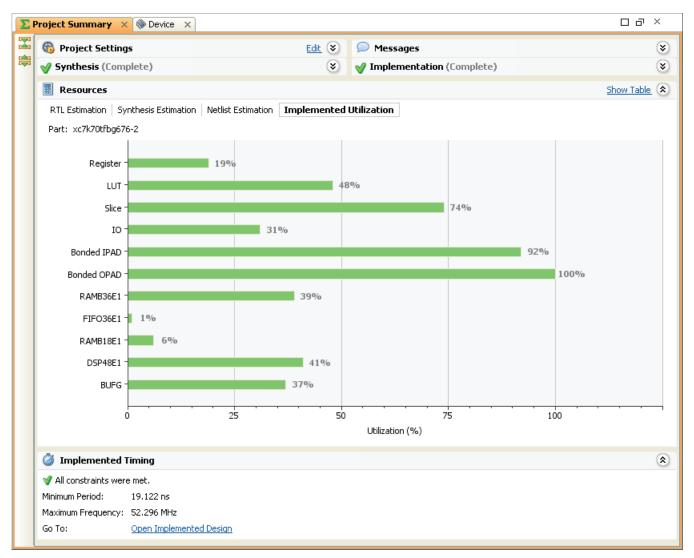

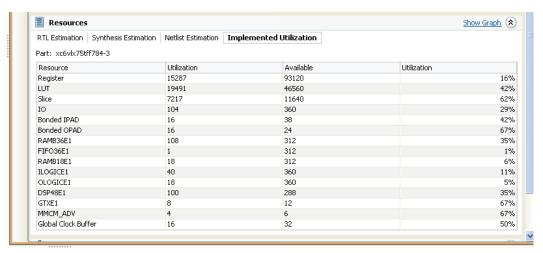

#### Adding Source Files or Directories