# **ISim User Guide**

UG660 (v14.3) October 16, 2012

This document applies to the following software versions: ISE Design Suite 14.3 through 14.6

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU "AS-IS" WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© Copyright 2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners. PCI, PCIe and PCI Express are trademarks of PCI-SIG and used under license

### **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                                                                                                                                               |

|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01/19/2011 | 13.4    | Date and Revision change only.                                                                                                                                         |

| 04/24/2012 | 14.1    | Updated Feature Support, page 3.                                                                                                                                       |

|            |         | Consolidated the Simulation chapters into Chapter 3, Compilation and Simulation.                                                                                       |

|            |         | <ul> <li>Consolidated fuse, vhpcomp, and vlogcomp Command Options, page 51 into a<br/>single table and created a top-level command cross-reference</li> </ul>          |

|            |         | <ul> <li>Added `uselib Verilog Directive in Chapter 3.</li> </ul>                                                                                                      |

|            |         | • Added -hil_zynq_ps Hardware Co-Simulation command to fuse command option in both Chapter 3, Compilation and Simulation, and Chapter 8, Using Hardware Co-Simulation. |

|            |         | <ul> <li>Consolidated VHDL Language Support Exceptions and Verilog Language<br/>Support Exceptions in Appendix B into two exceptions only tables.</li> </ul>           |

| 07/25/2012 | 14.2    | Revised one sentence in Chapter 3 to clarify 'uselib directive.                                                                                                        |

|            |         | Minor grammatical edits.                                                                                                                                               |

|            |         | Updated links in Appendix D, Additional Resources.                                                                                                                     |

| 10/16/2012 | 14.3    | Added a note to function_call that states "In named parameter association in a function_call slicing, indexing or selection of formals is not supported."              |

# Table of Contents

| Revision History                                    |

|-----------------------------------------------------|

| Chapter 1: Introduction to ISim                     |

| Simulation Libraries                                |

| Language Support.                                   |

| Feature Support                                     |

| Operating System Support                            |

| ISim Modes of Operation                             |

| Simulation Steps Overview                           |

| ISim Tutorials                                      |

| Chapter 2: Using the ISim GUI                       |

| ISim GUI Overview                                   |

| Setting ISim Preferences                            |

| Chapter 3: Compilation and Simulation               |

| Parsing Design Files                                |

| Project File Syntax 43                              |

| Predefined XILINX_ISIM Macro for Verilog Simulation |

| Simulating the Design 4                             |

| Mixed Language Simulation4                          |

| Timing Simulation (Gate-Level Simulation) 49        |

| ISim Executable Command                             |

| Pausing a Simulation                                |

| Saving Simulation Results 50                        |

| Closing Simulation 57                               |

| Chapter 4: Waveform Analysis                        |

| Working with the Wave Configuration                 |

| Customizing the Wave Configuration                  |

| Navigating the Wave Configuration                   |

| Printing Wave Configurations                        |

| Using Custom Colors                                 |

| Chapter 5: Viewing Simulation Results               |

| Waveform Databases and Configuration Files          |

| Opening a Static Simulation74                       |

| Chapter 6: Debugging at the Source Level                 |      |

|----------------------------------------------------------|------|

| Stepping Through a Simulation                            | . 77 |

| Using Breakpoints                                        | . 78 |

| Chapter 7: Writing Activity Data for Power Consumption   |      |

| Chapter 8: Using Hardware Co-Simulation                  |      |

|                                                          | 0.0  |

| Prerequisites                                            |      |

| Use Models                                               |      |

| Limitations                                              |      |

| Usage for Compilation                                    |      |

|                                                          |      |

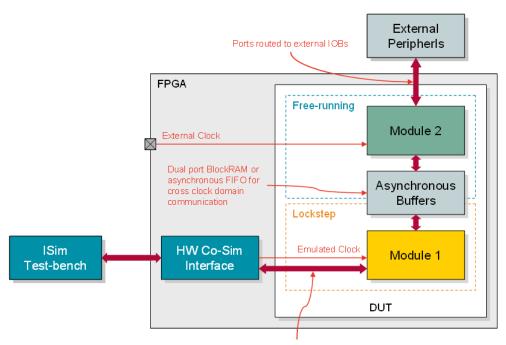

| Tools Flow                                               |      |

| Hybrid Co-Simulation Flow                                |      |

| Hardware Board Usage                                     |      |

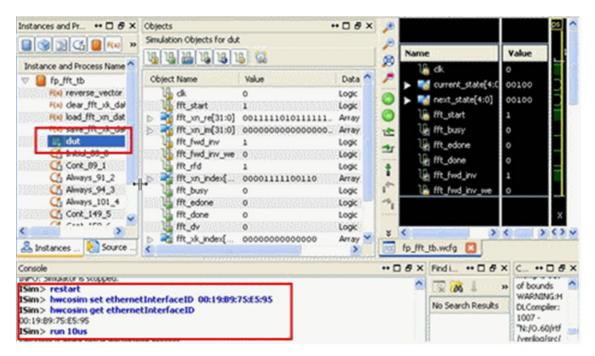

| Hardware Co-Simulation                                   |      |

| ISim Hardware Co-Simulation Tcl Commands                 |      |

| Board Support                                            |      |

| Frequently Asked Questions                               | . 95 |

| Chapter 9: ISim Tcl Commands                             |      |

| Aliasing Simulation Commands                             | 102  |

| ISim Wave Viewer Tcl Commands Overview                   | 103  |

| Command Line Conventions                                 | 103  |

| Tcl Commands                                             | 104  |

| Appendix A: Library Mapping File (xilinxisim.ini)        |      |

| Appendix B: Exceptions to VHDL and Verilog Language Supp | ori  |

| VHDL Language Support Exceptions                         |      |

| Verilog Language Support Exceptions                      |      |

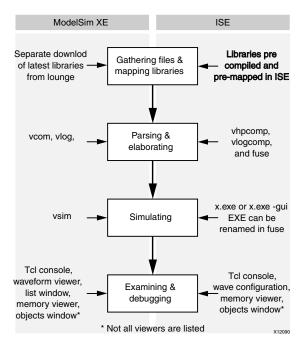

| Appendix C: Migrating from ModelSim XE to ISim           |      |

| About ModelSim XE                                        | 147  |

| About ISim                                               |      |

| Feature Comparison                                       |      |

| Simulation Process                                       |      |

|                                                          |      |

| Appendix D: Additional Resources                         |      |

| Xilinx Resources                                         | 157  |

| ISim Tutorials                                           | 157  |

# Chapter 1

## Introduction to ISim

Xilinx® ISim is a Hardware Description Language (HDL) simulator that lets you perform behavioral and timing simulations for VHDL, Verilog, and mixed VHDL/Verilog language designs.

This document describes the ISim tool features, lists the HDL languages that ISim supports, and explains the methods of interfacing with the tool. For easier navigation through this document, in your PDF reader, turn on **Previous View** and **Next View** buttons to navigate back and forth to linked information.

### **Simulation Libraries**

ISim uses precompiled simulation device libraries and updates those libraries automatically when updates are installed.

**Note:** Do *not* run the Simulation Library Compilation Wizard (Compxlib) to compile libraries for use with ISim.

### Language Support

ISim supports the following languages:

- VHDL IEEE-STD-1076-1993

- Verilog IEEE-STD-1364-2001

- Standard Delay Format (SDF) version 2.1

- VITAL-2000

### **Feature Support**

The following features are supported:

- Incremental compilation

- Source code debugging

- SDF Annotation

- VCD Generation

- Power analysis and optimization using SAIF

- Native support for HardIP blocks (such as MGT, PPC, andPCIe®)

- Multi-threaded compilation

- Hardware Co-Simulation (HWCoSim)

- Mixed VHDL/Verilog

- Memory Editor for viewing and debugging memory elements

- Single-click simulation re-compile and re-launch

- Easy to use, one-click compilation and simulation

- Built-in Xilinx simulation libraries

### **Operating System Support**

See the Xilinx Design Tools: Installation and Licensing Guide (UG798) for operating systems support.

The Xilinx Design Tools: Release Notes Guide (UG631) provides information about the most recent release changes. Links to these document are also available in Appendix D, Additional Resources.

### **ISim Modes of Operation**

ISim has two modes of operation:

- Graphical User Interface (GUI)

Provides a graphical view of simulation data. Menu commands, context commands, and toolbar buttons run simulation, and examine and debug data. For information about working with the GUI, see Chapter 2, Using the ISim GUI.

- Command line mode

Has no interaction with the GUI and you run commands at the command prompt.

After the simulation executable runs, a Tool Command Language (Tcl) prompt opens in which you can enter simulation Tcl commands to examine and debug data.

You can specify -tclbatch <file\_name> option to the simulation executable to run a set of Tcl commands after simulation has been loaded. You must have quit as the last Tcl command if you want the simulation to quit upon completion. For more information, see Chapter 3, Compilation and Simulation.

### **Simulation Steps Overview**

The steps for simulating a design in ISim are:

- Step 1: Gathering Files and Mapping Libraries

- Step 2: Parsing and Elaborating the Design

- Step 3: Simulating the Design

- Step 4: Examining the Design

- Step 5: Debugging the Design

### Step 1: Gathering Files and Mapping Libraries

The required files to run a simulation in ISim are as follows:

- Design files, including stimulus file

- User libraries

- Miscellaneous data files

### Stimulus File

Include an HDL-based test bench as the stimulus file. You can create or edit your test bench using any of the following:

- Text Editor: Create or edit an HDL test bench in any text editor.

- Language Templates:

Use a template to populate the file correctly, such as those available with the ISE tool.

For more information, see "Using the Language Templates" in ISE Help.

- Third-party tool: Create or edit an HDL test bench in any vendor-provided tool.

### **User Libraries**

Depending upon how you launch ISim, there are different methods available to add user libraries:

- When launching Project Navigator, define the user libraries in the ISE tool. See "Working with VHDL Libraries" in ISE Help for details.

- When using ISim standalone, interactive command mode, or non-interactive mode, set the library mapping file (see Appendix A, Library Mapping File (xilinxisim.ini) to point to your logical or physical libraries.

- When launching ISim from the PlanAhead tool, define the user libraries in that tool. See the *PlanAhead User Guide* (*UG632*) for more information. Appendix D, Additional Resources, contains a link to the document.

### Step 2: Parsing and Elaborating the Design

Before running a simulation, ISim must parse the code into one or more libraries, and then elaborate the design components upon which the design depends. The simulation executable is generated during this step.

### **GUI Mode**

When you invoke ISim from either the ISE or the PlanAhead tool, the ISim GUI is launched, the design is parsed, and design components are elaborated. For details, see "Simulation from ISE" in Step 3: Simulating the Design, or the *PlanAhead User Guide* (*UG632*). The design is parsed and elaborated manually at the command line, as described in the next section. Then you can invoke the generated simulation executable with the –gui mode to launch the GUI.

#### Interactive Command Line Mode

The steps in the interactive command-line mode:

- 1. Creating a project file. See Project File Syntax, page 43

- 2. Using the fuse command. See Running fuse, page 38

### Step 3: Simulating the Design

After design compilation and elaboration, the next step is to run the simulation executable, and simulate the design. For information about running simulation in read-only mode, see Opening a Static Simulation in Chapter 5.

### GUI Mode Simulation at the Command Line

After you generate a simulation executable (x.exe (default) or a user-specified name, you can run the simulation executable with the -gui switch on the command line; for example, my\_sim.exe -gui. This command launches the GUI. The simulation executable command does not start the simulation. To start the simulation, use one of the run simulation commands described in Simulating the Design, page 44.

You can then add signals to the Wave configuration. See Working with the Wave Configuration, page 59 for details.

Optionally, you can also invoke the simulation executable, launch the GUI, and run simulation with a Tcl file by leveraging the -tclbatch option, for example:

```

my_sim.exe -gui -tclbatch my_sim.tcl.

```

You can use the wave add command to add all signals at top-level of your my\_sim.tcl file to automatically trace the signals and display the signals in the GUI upon launch.

### Simulation from ISE

Parsing, elaboration, and running the simulation executable command is run in the background when you run one of the following processes in the ISE or the PlanAhead tool.

- Simulate Behavioral Model

- Simulate Post-Place & Route Model

These processes launch the GUI with the top-level signals being traced by default.

Optionally, you can specify custom Tcl files to control the signals that are traced when you launch the GUI.

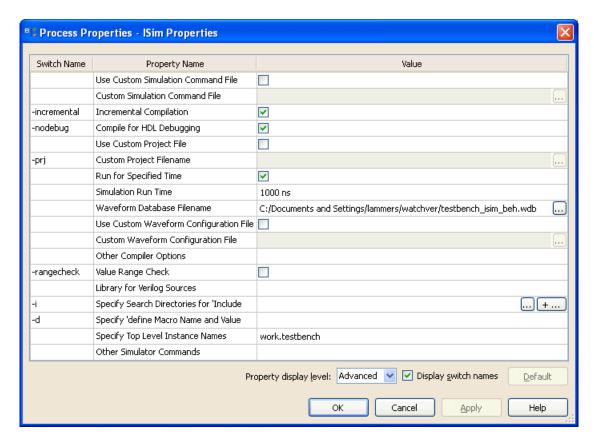

The simulator runs for the time specified under the ISE simulation process property, **Simulation Run Time**. See "Simulation Properties" in <u>ISE Help</u> for details.

To run for an additional time, use one of the run simulation commands described in Simulating the Design, page 44.

#### Interactive Command Line Mode

Run the simulation executable, for example, my\_sim.exe. When the Tcl prompt displays, type the run command.

Optionally, you can also invoke the simulation executable with a Tcl file by leveraging the -tclbatch option, for example, my\_sim.exe -tclbatch my\_sim.tcl.

Ensure that this step was run successfully. If not, see Examining Error Messages and Examining Log Files in Step 5: Debugging the Design.

### Step 4: Examining the Design

After the design is simulated, you debug the design to ensure that it meets the design specification.

You can examine the simulation results by:

- Viewing the signal interactions in the Wave window.

- Viewing or querying the results in the Console panel or the Tcl prompt.

In the debug phase, you can do the following:

- Save the results; see Saving Simulation Results, page 56.

- View and examine simulation results in a read-only static simulator; see Opening a Static Simulation in Chapter 5.

### Step 5: Debugging the Design

If you encounter issues, you must debug the design to identify the root cause and the resolution of the issues. ISim provides a variety of ways to debug the design. To debug your design, examine the error messages and log files.

### **Examining Error Messages**

First, look at the error messages to see if there are any errors in the design. Error messages appear in the ISE tool Console (GUI mode) and the log files discussed in the next section. Look for messages with one of the following prefixes:

- HDL Compiler

- Indicates an error during the parsing or static elaboration step. If an error occurs during parsing and elaboration, and this step was not run successfully, the problem can be an HDL compiler issue. Type fuse -v 1 to dump information that might help identify the problem. A fuse.log file that contains a list of error messages and errors appears in the ISE tool Console (in ISE Integration Mode).

- Simulator Indicates an error during executable code generation or simulation. See Step 3: Simulating the Design, page 6. Use the file name and line number in the message to locate the issue.

### **Examining Log Files**

Examining the available log files can provide helpful clues about design errors. The following log files are available:

- fuse.log

Log file containing output produced by the fuse command during the parsing and elaboration step.

- isim.log

Log file containing output produced by simulation executable during the simulation step. This file does not disclose any design data, and is safe to share with Xilinx Technical Support if you report a problem.

- isimcrash.log

Log file generated when the tool encounters an unexpected error or condition.

This is generated inside the

- $./{\tt isim}/{<} {\it simulation\_executable}{\gt}. {\tt sim directory}.$

Provide this file to Xilinx® Technical Support for further assistance. This file also does not disclose any design data, and is safe to share with Xilinx Technical Support if you report a problem.

### Using Tcl Simulation Commands

Several simulation commands are available to assist you with debugging. The following commands are linked to the full command description, and can be run at the command line Tcl prompt, or in the Console panel.

- isim ptrace on

- isim ltrace on

- dump

- show

- isim force

- bp

- onerror

For debug strategies, see Chapter 6, Debugging at the Source Level.

For more commands, see Chapter 9, ISim Tcl Commands.

### **ISim Tutorials**

See the following tutorials for more information:

- *ISE Simulator (ISim) In-Depth Tutorial (UG682)*Demonstrates how to use ISim for design simulation and debugging.

- ISE Hardware Co-Simulation Tutorial: Accelerating Floating Point FFT Simulation (UG817) Shows how to use the ISim Hardware Co-Simulation (HWCoSim) feature to accelerate Floating Point FFT simulation.

Appendix D, Additional Resources, provides links to these documents.

## Chapter 2

# Using the ISim GUI

The ISim Graphical User Interface (GUI) consists of the main window, which contains panels, the Workspace, toolbars, and the status bar. In the main window, you can:

- View the parts of the design that can be simulated

- Add and view signals in the wave configuration

- Use commands to run simulation

- Examine the design, and debug as necessary

### **ISim GUI Overview**

The ISim GUI launches when you run the simulation executable from the ISE® tool, the command line, or the PlanAhead<sup>TM</sup> tool.

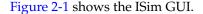

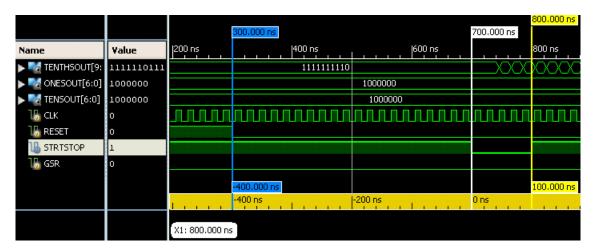

Figure 2-1: ISim GUI

To close ISim, select **File > Exit**. ISim prompts you to save your waveform configuration before closing.

Table 2-1 lists the ISim GUI components as idenfied in Figure 2-1, page 9, and links to the GUI part description.

**Note:** In your PDF reader, turn on **Previous View** and **Next View** Buttons to navigate back and forth to linked information.

Table 2-1: ISim GUI Components

|     | GUI Part by #                                   | Description                                                                                                                                                                                                               |

|-----|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | Menus and Toolbar:<br>Commands and<br>Shortcuts | Provides access to most operations available in the tool. Some operations are available in context menu only.                                                                                                             |

| 2.  | ISim Menu and<br>Toolbar                        | Provides access to frequently used commands.                                                                                                                                                                              |

| 3.  | Instances and<br>Processes Panel                | Displays the block (instance and process) hierarchy associated with the current simulation.                                                                                                                               |

| 4.  | Source Files Panel                              | Displays the list of all the files associated with the design.                                                                                                                                                            |

| 5.  | Console Panel                                   | Displays messages generated by the simulator. You can enter simulation Tcl commands at the prompt.                                                                                                                        |

| 6.  | Breakpoints Panel                               | Displays a list of all breakpoints currently set in the design.                                                                                                                                                           |

| 7.  | Find in Files Results<br>Panel                  | Displays the results that match a text string in a set of files.                                                                                                                                                          |

| 8.  | Search Results Panel                            | Displays the results that match the criteria from a search                                                                                                                                                                |

| 9.  | Objects Panel                                   | Displays the simulation objects associated with the block selected in the Instances and Processes panel.                                                                                                                  |

| 10. | Wave Window                                     | Displays the wave configuration, which consists of a list of signals and buses, their waveforms, and any wave objects, such as dividers, cursor or markers. The Wave window can display more than one wave configuration. |

| 11. | Text Editor Window                              | Displays read-only Hardware Description Language (HDL) files.                                                                                                                                                             |

| 12. | Status Bar                                      | Displays a brief description for a menu command or toolbar button that your cursor is placed over, and the simulation time.                                                                                               |

The following subsections describe each ISim GUI component.

### Menus and Toolbar: Commands and Shortcuts

The ISim main window consists of functionally different toolbars that reflect the most commonly used Main menu options.

The Main menu provides extended options within the option categories. The main window toolbar buttons are below the Main menu at the top of the user interface.

To show or hide toolbars, select **View > Toolbars >** <toolbar\_name>.

### File Menu and Standard Toolbar

The Standard toolbar provides access to frequently used File menu commands.

The File menu and the Standard toolbar provide access to the following options:

#### New

Use the New dialog box and to select the type of file you want to create. You can open a new text file, schematic, or symbol.

#### Open

Use this option to browse through your directories and select a file to open. The file displays in the appropriate application or editor.

#### Save

Use this option to save the active file to disk and overwrites the previously saved version. If a file is not saved previously, the Save As dialog box opens and lets you save the active file to disk.

#### Save All

Use this option to save all files that require saving.

#### Print

Use the Print dialog box to print an active file.

### Edit Menu and Toolbar

The Edit toolbar provides access to frequently used Edit menu commands.

Cut, Copy, Paste, Delete are available as well as Undo, Redo, Find, and Find in File.

#### View Menu and Toolbar

The View toolbar provides access to frequently used View menu commands.

View toolbar options are as follows:

- Zoom In and Zoom Out, Set View for all content to be visible, and Zoom to Cursors.

- The **Refresh** button cleans up the display of the file in focus.

In the View menu, additional options are:

#### Panel

Opens a dialog box with the following check box options: Search Results, Find in Files Results, Breakpoints, Compilation Log, Source Files, Memory, Objects, Instances and Processes, Console.

### Toolbars

Turn the toolbars on and off.

• A check box controls the use of the Status Bar.

### ISim Menu and Toolbar

The ISim toolbar provides access to frequently used ISim commands.

Table 2-2 describes the Simulation toolbar options:

Table 2-2: Simulation Toolbar Options

| Button            | Description                                                                                                 |

|-------------------|-------------------------------------------------------------------------------------------------------------|

| <u>ı</u> <u>←</u> | Moves the main cursor to the nearest marker to the left of the current position of the marker.              |

| <b>⊉</b> r        | Moves the main cursor to the nearest marker to the right of the main current position of the marker.        |

| +                 | Adds a marker at the position of the main cursor to the Waveform area.                                      |

|                   | Resets the simulation time to zero.                                                                         |

| •                 | Runs simulation until there are no more events, a stop command is issued or a break point is encountered.   |

| ×                 | Runs simulation for the amount of time specified (Run For).                                                 |

| 1.00us 🔻          | Specifies the amount of time the simulation runs.                                                           |

| <b>Ģ</b> ≣        | Steps through the simulation to the next line of HDL code.                                                  |

| II                | Forces a running simulation to stop immediately. Simulation can be restarted using one of the run commands. |

|                   | Ends the current simulation, leaving the simulation data open.                                              |

| Re-launch         | Relaunch Simulation.                                                                                        |

### Window Menu and Toolbar

The Window toolbar provides access to frequently used Window menu commands.

The Window toolbar options are the standard options to cascade, tile, show side-by-side, and bring to front.

### Help Toolbar

The Help toolbar provides access to frequently used Help menu commands. Support and Services displays the Xilinx® Support page in the default web browser.

**What's This?** activates tooltips. After clicking this button, you can hover over a menu item or button and get a brief description of its functionality.

### **Keyboard Shortcuts**

Table 2-3 lists the ISim keyboard shortcuts.

Table 2-3: Keyboard Shortcuts

| Shortcut           | Menu Command               |

|--------------------|----------------------------|

| F1                 | Help Topics (Help menu)    |

| F3                 | Find Next (Edit menu)      |

| F5                 | Run All (View menu)        |

| F6                 | Zoom Full View (View menu) |

| F7                 | Zoom Out (View menu)       |

| F8                 | Zoom In (View menu)        |

| F11                | Step                       |

| Delete             | Delete (Edit menu)         |

| Ctrl+N             | New (File menu)            |

| Ctrl+O             | Open (File menu)           |

| Ctrl+S             | Save (File menu)           |

| Ctrl+P             | Print (File menu)          |

| Ctrl+Z             | Undo (Edit menu)           |

| Ctrl+Y             | Redo (Edit menu)           |

| Ctrl+X             | Cut (Edit menu)            |

| Ctrl+C             | Copy (Edit menu)           |

| Ctrl+V             | Paste (Edit menu)          |

| Ctrl+F             | Find (Edit menu)           |

| Ctrl+G             | Go To (Edit menu)          |

| Ctrl+A             | Select All (Edit menu)     |

| Ctrl+W             | Add To Wave Configuration  |

| Ctrl+F4            | Close (Window menu)        |

| Ctrl+Tab           | Next (Window menu)         |

| Ctrl+Shift+Tab     | Previous (Window menu)     |

| Ctrl+Home          | Go To Time 0               |

| Ctrl+End           | Go To Latest Time          |

| Ctrl+Shift+F5      | Restart                    |

| Ctrl+ Mouse Wheel  | Zooms in and out           |

| Shift+ Mouse Wheel | Zooms left and right       |

Table 2-3: Keyboard Shortcuts (Cont'd)

| Shortcut    | Menu Command        |

|-------------|---------------------|

| Mouse Wheel | Scrolls up and down |

| Left        | Previous Transition |

| Right       | Next Transition     |

| Pause       | Break               |

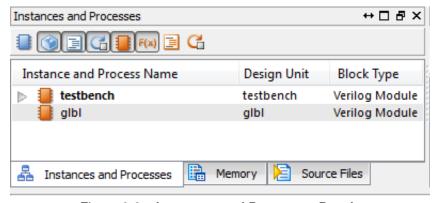

### Instances and Processes Panel

The Instances and Processes panel displays the block (instance and process) hierarchy associated with a wave configuration that is open in the Wave window. Instantiated and elaborated entities and modules display in a tree structure; components being entities, processes, tasks, and blocks.

The columns in this panel are:

#### Instance and Process Name

Shows the instance, process, and static tasks or functions buttons in a tree structure showing the block hierarchy of the design.

### Design Unit

Displays the names of the design units (Verilog module or VHDL entity architecture) corresponding to the instance, static task or function, or process from the first column.

### • Block Type

Displays the type of the instance, static task or function, or process (for example, Verilog Module).

The Instances and Processes tabs are:

#### Instance

Displays the instance, process, and static tasks or functions buttons in a tree structure showing the block hierarchy of the design.

#### Memory

Displays the memory of the design object. See Using the Memory Editor, page 26.

#### Source Files

Lists the source files of the design.

Figure 2-2, page 14 shows the Instances and Processes panel.

Figure 2-2: Instances and Processes Panel

### Design Hierarchy Buttons

Table 2-4 describes the design hierarchy buttons in the Instances and Processes panel.

Table 2-4: Instance and Processes Panel Buttons

| Icon               | Represents                                |

|--------------------|-------------------------------------------|

|                    | VHDL Entity                               |

| <b>③</b>           | VHDL Package                              |

| l <sup>III</sup> I | VHDL Block                                |

| G                  | VHDL Process                              |

|                    | Verilog Module                            |

| F(x)               | A toggle for filtering Verilog tasks.     |

|                    | A toggle for filtering Verilog blocks.    |

| G                  | A toggle for filtering Verilog Processes. |

With Hierarchy buttons you can take the following actions:

- To expand a hierarchy to display its components, click the arrows or use the **Expand** context menu commands (see Expanding and Collapsing a Hierarchy, page 16).

- To sort the information in this panel according to the data in one of the columns, click the column title, such as **Design Unit**.

- To hide or restore the panel, select **View > Panel > Instances and Processes**.

1

### Expanding and Collapsing a Hierarchy

You can expand and collapse a hierarchy in any window or panel with objects in nested groups using one of the following methods:

- Clicking the arrows:

- Click the expand arrow to expand the hierarchy. One level can be expanded at a time.

- Click the collapse arrow to collapse the hierarchy.

- Using the menu command:

- 1. Select an object.

- 2. Select Edit > Wave Objects >

- Expand

Expands the hierarchy object that is selected. One level can be expanded at a time.

Collapse

Collapses the hierarchy of the object selected.

- Using the context menu:

- 1. Select an object.

- 2. Right-click and select the applicable command from the context menu.

### Arranging the Main Window

You can move windows, panels, and the toolbar around in the interface using one of the following techniques:

Using Window Commands

The Window menu commands are available for the Wave window and Text Editor window only.

Using Drag and Drop

For other parts of the interface, like panels and the main window toolbar, drag and drop lets you move the object to a new location. To do so:

- 1. Click and hold the header for the panel to move.

- 2. Move the panel to a new location.

A gray box indicates where the panel is placed.

3. Release the mouse button to place the panel to the new location.

### Hiding and Restoring Windows

Many of the parts of the main window can be hidden from view, and restored again.

Note: To restore windows to their default locations, select View > Restore Default Layout.

Standard minimize, maximize and close commands apply to the Wave window and Text Editor window using the upper right-hand buttons.

With these commands, you can hide, restore, float, and dock the panel. Table 2-5 lists the buttons and description.

Table 2-5: Panel Control Buttons

| lcon | Description                                                                                                                                                             |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ++   | Toggle Slide Out Minimizes the panel. Also used to restore the pane by hovering over the name of the panel at the edge of the window, and clicking the minimize button. |

|      | Toggle Maximized Maximizes the panel. Click again to restore the panel size.                                                                                            |

| 8    | <b>Toggle Floating</b> Floats the panel. Re-click to restore to its former location.                                                                                    |

| ×    | Close Closes the panel from view. To restore the panel, select View > Panels and select the pane to restore to view.                                                    |

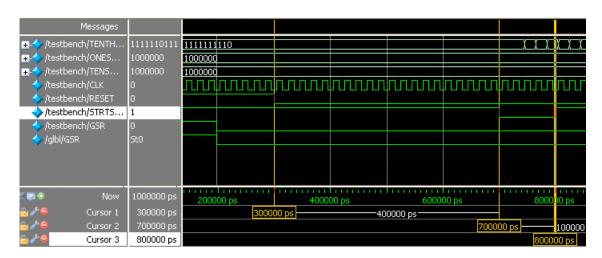

### Wave Window

The Wave window displays signals, buses, and their waveforms. Each tab in the Wave window shows a wave configuration that contains a list of signals and buses, their properties, and any added wave objects such as dividers, cursors, and markers.

In the GUI, the signals and buses in the wave configuration are traced during simulation, and you use the wave configuration to examine the simulation results. The design hierarchy and the signal transitions are not part of the wave configuration, and are stored in a separate database .wdb file.

### Wave Configuration File (.wcfg)

A wave configuration comprises a list of signals; their properties, such as color and radix value; and other wave objects, such as dividers, groups, markers and cursors. You can completely customize a wave configuration: you can add or remove signals and other wave objects at any time when the simulation is not actively running.

The initial file, Default.wcfg, is not saved until you save the file. The wave configuration file stores the list of signals, their properties, and wave objects.

You can create and simulate multiple wave configurations, and the wave configurations can be saved separately.

For information about saving the Wave Configuration, see Saving Wave Configurations, page 23.

When you invoke the simulator from any mode, it creates the Default.wcfg file. You must supply a filename to save a wave configuration file to the disk as a .wcfg file.

- In GUI mode, when ISim exits, it prompts you to type a filename in the **Save As** dialog box.

- In batch mode, type **wcfg save** to save the contents of the Default.wcfg before exiting the ISim tool.

### **Active Window**

When you invoke the simulator, the first active window is Default.wcfg. You can change the active window by clicking the window tab or using the wave add command.

- In the GUI, select **File > New** or **File > Open** to change the active window to the newly created waveform configuration window.

- In Tcl, the wcfg new and wcfg open commands change the active window to the newly created window just like File > New and File > Open.

### Wave Configuration Signal and Bus Buttons

The signals and buses in the Wave window can be one of the following design objects with the corresponding icon.

Table 2-6 lists the ISim signal buttons. Table 2-7, page 19 lists the Bus signal buttons.

Table 2-6: ISim Signal Buttons

| Icon           | Description                         |

|----------------|-------------------------------------|

| ч              | Input Port                          |

| Ц              | Output Port                         |

| 170            | InOut, Bidirectional Port           |

| ų,             | Internal Signal                     |

| U              | Constants, parameters, and generics |

| U <sub>b</sub> | Variable                            |

| Щ              | Linkage Signal (VHDL only)          |

| ų              | Buffer Signal                       |

Table 2-7 lists the ISim Bus buttons.

Table 2-7: ISim Bus Buttons

| Button     | Description                             |

|------------|-----------------------------------------|

| <u> </u>   | Input Bus                               |

| <b>*</b>   | Output Bus                              |

| 170        | InOut, Bidirectional Bus                |

| ₽6         | Internal Bus                            |

| <b>™</b> 6 | Constants, Parameters, and Generics Bus |

| ■6         | Variable Bus                            |

| <b>E</b>   | Linkage Bus                             |

| ₩          | Buffer Bus                              |

### Objects in the Wave Configuration

#### Cursors

The main cursor and secondary cursor in the wave configuration are used to pinpoint a time (main cursor) and to measure time (main and secondary cursors together). The cursors form the focal point for various navigation activities.

### Main Cursor

The main cursor is a solid line that intersects the waveform, and the value at that intersection is displayed in the **Value** column for each waveform. The cursor is the current simulation time while simulation is running, with the time displayed directly above the cursor. See Cursors in Chapter 4.

### • Secondary Cursor

The secondary cursor is a dotted line used with the main cursor to identify a time range. The time range can be used with zoom and print to focus on the area.

#### Markers

A marker is used to mark a particular time for future reference. A marker is a vertical line intersecting the waveform. A marker lets you display the signal value where the marker intersects the waveform. The time of the marker displays at the top of the line. In addition, a series of markers can be used to jump the cursor forward or back for quick analysis of value change. See Markers in Chapter 4.

### Adding Markers and Displaying Waveform Values With Markers

#### Hollow/Filled-in Circle

When placing or moving cursors and markers, you can use the **Snap to Transition** button to assist with placing the cursor/marker more precisely on a signal transition.

• When placing or moving a cursor or marker, the mouse displays a hollow circle.

• When hovering over the signal transition, the mouse displays a filled in circle when hovering over a transition of a signal.

#### Dividers

A divider is a visual separator of signals in the wave configuration.

### Groups

A group is a virtual collection to which you can add signals and buses in the wave configuration as a means of organizing a set of related signals. A group displays the group icon and group name.

The group itself displays no waveform data but can be expanded to show its contents or collapsed to hide them. See Adding a Group in Chapter 4.

#### **Virtual Buses**

A virtual bus is a grouping to which logic scalars and arrays can be added. A virtual bus displays the icon and virtual bus name. The virtual bus displays a bus waveform, which is comprised of the signal waveforms in the vertical order that they appear under the virtual bus, flattened to a one-dimensional array. See Adding Virtual Buses in Chapter 4.

#### Wave Window Toolbar Buttons

Table 2-8 shows and describes the wave window toolbar buttons.

Table 2-8: Wave Window Toolbar Buttons

| Button   | Description                                                                                                                                                                                                                               |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P        | Zoom Out decreases the size of the viewed objects.                                                                                                                                                                                        |

| <b>Æ</b> | Zoom In increases the size of the viewed objects.                                                                                                                                                                                         |

| Ø        | Zoom to Full View zooms out to display the entire view in the active window.                                                                                                                                                              |

| <u>"</u> | Zoom to Cursors displays the waveforms such that the two cursors are at the left and right edge of the display. If the secondary is off, the command centers the display around the main cursor without changing the magnification level. |

| <b>(</b> | Go To Time 0 moves the cursor and focus to O time.                                                                                                                                                                                        |

Table 2-8: Wave Window Toolbar Buttons (Cont'd)

| Button     | Description                                                                                                                                      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>(2)</b> | Go To Latest Time moves the cursor and focus to the end of simulation.                                                                           |

| <b>±</b>   | Go To Next Transition moves the main cursor to next transition.                                                                                  |

| 14         | Go To Previous Transition moves the main cursor to the previous transition.                                                                      |

| t          | Adds a marker at the position of the main cursor to the Waveform area.                                                                           |

| Ť          | Moves the main cursor to the nearest marker to the left of the current position.                                                                 |

| S          | Moves the main cursor to the nearest marker to the right of the current position.                                                                |

| 47         | Swaps the main and secondary cursors, if both are set.                                                                                           |

| 'n         | Snap to Transition Mode moves the cursor to a transition when you place the cursor close to the transition. This mode can be switched on or off. |

| 111        | Displays and hides the floating ruler that can be moved to the desired location in the Wave window.                                              |

### Working With Wave Configurations

You can create any number of Wave Configurations in the current session. The Wave Configuration stores the list of signals, their properties and any wave objects that were added.

To create a wave configuration:

- 1. Select **File > New.**

- The New dialog box opens.

- 2. Select **Wave Configuration** from the list.

- 3. Click OK.

A new untitled wave configuration opens. The new wave configuration is empty until you add signals (see Adding Signals to the Wave Configuration.)

If more than one wave configuration is open, either:

- Use the wave configuration tab to locate a particular wave configuration.

- Select Window > Next or Window > Previous to navigate through open wave configurations.

### Adding Signals to the Wave Configuration

You can populate the Wave window with the signals from your design using menu commands or drag and drop capabilities in the GUI, or using Tcl commands in the Console panel.

**Note:** Changes to the wave configuration, including creating the wave configuration or adding signals, do not become permanent until you save the WCFG file. For more information, see Wave Configurations and WCFG Files.

#### In the GUI:

- 1. In the Instances and Processes panel, expand the design hierarchy, and select an item. The objects that correspond to the selected instance or process displays in the Objects panel.

- 2. In the Objects panel, select one or more objects.

- 3. Use one of the following methods to add objects to the wave configuration:

- Right-click, and select Add to Wave Window from the context menu.

- Drag and drop the objects from the Objects panel to the Name column of the Wave window.

- In the Console panel, use wave add command.

### **Using Tcl:**

- Optionally, you can first identify the objects you want to add by exploring the design hierarchy in the Instances and Processes panel and the Objects panel, or by entering the scope command in the Console panel.

- In the Console panel, enter the wave add command to enter an individual object or a group of objects.

### Wave Configurations and WCFG Files

Although both a wave configuration and a WCFG file refer to the customization of lists of waveforms, there is a conceptual difference between them:

- The wave configuration is an object that is loaded into memory with which you can work.

- You can name a wave configuration or leave it untitled. The name appears on the tab of the wave configuration window.

- When saving a wave configuration to a WCFG file using a GUI Tcl command, the WCFG file takes the name supplied as a command argument.

- When loading a wave configuration from a WCFG file, the wave configuration displays the name of the file.

- The WCFG file is the saved form of a wave configuration on disk.

### Saving Wave Configurations

You can save the current wave configuration, and if you have multiple wave configurations open, each can be saved to a unique name for later viewing.

To save a wave configuration, do one of the following:

- Select File > Save

- Press Crtl+S

- Click the **Save** button

Note: Use File > Save As to assign a different name to the wave configuration.

### Searching For Objects

You can search for objects in the design using the **Search** command, which is available in the Instances and Processes panel and in the Objects panel. Search criteria includes a text string, and/or an object-type filter.

To search for objects, do the following:

- 1. Place the cursor in the Objects panel or the Instances and Processes panel.

- 2. Right-click and select Search from the context menu.

- 3. In the **Search** dialog box, enter a text string. You can use an asterisk, \*, as a wildcard symbol.

- 4. Select the object type for which you are searching. Click **Match case** if applicable.

- 5. Click **OK**.

Objects that match the search criteria display in the Search Results Panel.

### Opening HDL Source Files

You can open Hardware Description Language (HDL) source file in the ISim Text Editor.

To view an HDL source file, do the following:

- 1. In the Instances and Processes panel, the Objects panel, or the Source Files panel, select a file

- 2. Double-click the file, or right-click and select **Go To Source** from the context menu. The HDL source file associated with that object opens in the Text Editor.

When you open a file using the **File > Open** menu command, the file is in write mode.

In the **Open** dialog box, change **Files of type** file to Verilog or VHDL, select the file, and click **Open**. See Modifying Source Files, page 26.

### Source Files Panel

The Source Files panel displays as a tab in the Instances and Processes panel. When you select the tab, it displays list of files associated with the design. The list of files is provided by the fuse command during design parsing and elaboration, which is run in the background for GUI users.

To open a source code file, do the following:

- 1. Select a file in the list.

- 2. Click the **Go To Source Code** button.

### **Objects Panel**

The Objects panel displays all simulation objects (ports, signals, variables, constants, parameters, and generics) associated with the selected instances and processes in the Instances and Processes panel.

The top of the panel displays which instance or process is selected in the Instances and Processes panel; those objects and their values are listed in the Objects panel.

The table columns are defined as follows:

### Object Name

Displays the name of the simulation object, accompanied by the symbol which represents the type of object.

#### Value

The value of the simulation object at the current simulation time or at the main cursor, as determined by the **Sync Time** button.

#### Data Type

Displays the data type of the corresponding simulation object, logic or an array.

Toggle buttons are available in the Objects panel, as described in Table 2-9.

Table 2-9: Object Panel Toolbar Buttons

| Button     | Description                                                 |

|------------|-------------------------------------------------------------|

| ι <u>μ</u> | Toggles the input ports on and off.                         |

| ų.         | Toggles the output ports on and off.                        |

| IIO        | Toggles the inout, bidirectional ports on and off.          |

| 1/0        | Toggles the internal signals on and off.                    |

| U          | Toggles the constants, parameters, and generics on and off. |

Table 2-9: Object Panel Toolbar Buttons (Cont'd)

| Button | Description                                                                                                                                                                                                                                                |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18     | Toggles the variables on and off.                                                                                                                                                                                                                          |

|        | <ul> <li>Toggles the Sync Time feature on and off.</li> <li>When on, Objects panel values are based on the main cursor in the Wave window.</li> <li>When off, values are the values at the Sim Time in the Status Bar (at simulation end time).</li> </ul> |

### Using Show Drivers

You can use the **Show Driver** command to display the driver for a change in signal, or object value. This command is used to determine the cause of a value change, which helps determine if circuit connections are correct. ISim displays the signal, or object, and its one or more drivers in the Console panel.

The Show Driver command is available for probing objects in the following areas:

- Objects panel

- Wave window

- Console panel (using the show driver command)

To show drivers:

- 1. Select an object, or signal.

- 2. Select Edit > Wave Objects > Show Drivers.

The Console panel lists the drivers for the object or signal. When there is no driver, a message indicates that there is no driver.

*Note:* Running this command is the same as running show driver at the Console panel prompt.

### Showing Display Elements

In the Objects panel, you can control whether or not to limit a preset maximum number of child elements displayed for every composite object. You can change the preset maximum number using the Preferences dialog box.

To display all child elements:

- 1. Right-click anywhere in the object list in the Objects panel.

- 2. Right-click, and select **Show All Elements**.

The number of children in the object hierarchy display.

To limit the display of child elements, right-click anywhere in the object list in the Objects panel, and select **Limit Elements**.

To change the preset maximum number of child elements, set the preference settings as follows:

- 1. Select **Edit** > **Preferences**.

- 2. In the **Preferences** dialog box, select **ISim Simulator**.

- 3. Select Limit the maximum number of elements displayed to, and enter a number.

- 4. Click **Apply**, and **OK**.

### Selecting an Object in the Wave Window

To highlight signals for an object in the Objects panel:

- 1. Select an object in the Objects panel.

- 2. Right-click, and choose **Select in Wave Window**.

### Text Editor Window

The Text Editor window is available for access to the underlying HDL source files.

### Modifying Source Files

To modify source files:

- 1. Open the source file in the ISim Text Editor.

- 2. Make the appropriate edits, and run **Re-Launch** to re-simulate the design.

The ISE project automatically saves the source file changes.

### **Setting Breakpoints**

You can set breakpoints in executable lines in your HDL file so you can run your code continuously until the source code line with the breakpoint is reached, as described in Using Breakpoints in Chapter 6.

**Note:** You can set breakpoints on lines with executable code only.

### Using the Memory Editor

The Memory Editor lets you find and change contents of two-dimensional memory arrays in a design during simulation (without recompiling or re-elaborating the design). There are three places that show memory objects: the Memory tab, the Object panel, and the Search Result tab. To open the Memory Editor, follow one of these methods.

- On the Memory tab which contains all the two-dimensional arrays of logic types in a design, double-click a displayed memory object.

- In the Objects panel, right-click a two-dimensional array of logic type, and select **Memory Editor** from the context menu.

- In the Instance and Processes panel, run a search on a memory name. When the searched memory displays in the Search Results panel, you can right-click the memory and select **Memory Editor** from the context menu.

**Note:** For objects that are not two-dimensional array of a logic type, the Memory Editor choice in the Context Menu is grayed out.

The Memory Editor displays the following fields:

### Address

Go to a particular location in the displayed memory.

#### Columns

Controls the display of the number of elements per row. The auto column displays the maximum of 2 to power N of elements.

### Address Radix

Controls the radix of the address displayed in the Memory Editor.

#### Value Radix

Controls the radix of the display value in the Memory Editor.

You can float the Memory Editor window and the Memory Editor retains the previous state after the float operation.

You can navigate inside Memory Editor with the arrow keys, the current position of a selected item displays on the status bar based on the current address radix.

### Console Panel

The Console panel lets you view a log of commands generated by ISim, and enter standard and ISim-specific Tcl commands at the command prompt. The Console panel shows:

### Messages

Generated messages include errors, warnings, and informational messages. The Console panel also echoes simulator commands that were invoked from the graphical controls in the ISim GUI.

#### Simulation commands

The command prompt lets you enter simulation Tcl commands, and to view the command dump (or print-out) in the Console panel. See Simulating the Design in Chapter 3.

A number of right-click menu commands are available to help manage the contents of the Console panel.

### **Breakpoints Panel**

A breakpoint is a user-determined stopping point in the source code used for debugging a design with ISim. The Breakpoints panel displays a list of breakpoints that are set in the design. See Using Breakpoints in Chapter 6.

For each breakpoint set in your source files, the list in the Breakpoints panel identifies the file location, filename, and line number. You can delete a selection, delete all breakpoints, and go to the source code from either the Breakpoint panel toolbar buttons or the context menu.

To set a breakpoint, use one of the following options:

- Select View > Breakpoint > Toggle Breakpoint.

- Click the Toggle Breakpoint button.

- In the HDL file, click a line of code just to the right of the line number.

Alternatively, you can right-click a line of code, and select **Toggle Breakpoint**.

After the procedure completes, a simulation breakpoint icon appears next to the line of code.

ZIM)

A list of breakpoints is available in the Breakpoints panel. If you place a breakpoint on a line of code that is not executable, the breakpoint is not added.

To remove the breakpoint click the breakpoint.

### **Breakpoint Toolbar Buttons**

Table 2-10 describes the Breakpoint buttons.

Table 2-10: Breakpoint Buttons

| Button     | Description                                                                                               |

|------------|-----------------------------------------------------------------------------------------------------------|

| ×          | Deletes the selected line from the Breakpoint panel, and deletes the breakpoint from the HDL source file. |

| <b>2</b>   | Deletes all breakpoints from the HDL source files.                                                        |

| <u>.</u> o | Opens the HDL source file in the text editor with the breakpoint in focus.                                |

### Search Results Panel

The Search Results panel displays the results that match the search criteria from the Search command. The results display the icon for the object type being displayed and the location of the object in the design.

### Search Results Toolbar Command Buttons

Table 2-11 shows and describes the buttons available in the Search Results panel.

Table 2-11: Search Results Toolbar Buttons

| Button   | Description                                                                                              |

|----------|----------------------------------------------------------------------------------------------------------|

| <b></b>  | Clears the contents of the Search Results panel.                                                         |

| Пþ       | Adds the signal associated with the selected search result to the wave configuration in the Wave window. |

| ≣,0      | Opens the HDL source file in the text editor at the line where the design unit is defined.               |

| I.I      | Opens the HDL source file in the text editor at the line where the design unit is instantiated.          |

| <b>⊗</b> | Stops the search.                                                                                        |

www.xilinx.com

#### Find in Files Results Panel

You can find a text string in a set of files as follows.

To use the **Find in Files** options:

Table 2-12: Find in File Buttons and Actions

| Button  | Action                                                                                                                                 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|

|         | Select <b>Edit &gt; Find in Files</b> , or click the <b>Find Text in Files</b> button.                                                 |

| Ø.      | In the <b>Find in Files</b> dialog box, specify the text to find, set the parameters for your search, and click <b>Find</b> .          |

|         | In the Find in Files Results panel, do any of the following:                                                                           |

| <b></b> | To clear all results from the panel, click the <b>Clear All</b> button.                                                                |

| =       | To open the file that contains the find result in the Workspace, select a find result, and click the <b>Show Current Result</b> button |

|         | Alternatively, you can double-click the find result to open the file.                                                                  |

| 1       | To view the next find result, click the <b>Show Next Result</b> button.                                                                |

| î       | To view the previous find result, click the <b>Show Previous Result</b> button.                                                        |

| <       | To stop the currently running Find in Files search, click the <b>Stop Job</b> button.                                                  |

|         | To save your Find in Files search results to a Comma Separated Value (CSV) file, click the <b>Save Results as a Text File</b> button.  |

### Re-launching Simulation

The Re-launch button lets you re-launch the ISim simulation after making a modification in an Hardware Description Language (HDL) file to fix an identified issue. You also can recompile from the ISim GUI.

Recompile and Re-launch are fully automated features. The dialog box messages specify where an issue is located. Re-launch keeps all the options as set at compile time, and automatically runs simulation to the specified runtime when the flow was launched from either the Project Navigator or the PlanAhead tool.

- When you successfully re-launch a simulation, your simulation completes without errors.

- When you re-launch an unsuccessful simulation, a dialog box opens with the syntax

error failure to the compiled source code. The links go to the source code with errors

in the source window. It is recommended that you address the linked errors

sequentially to correct the issues and then recompile using the Re-launch button to

verify the fix.

### Applying Stimulus

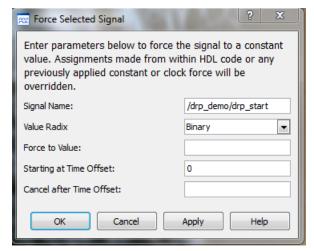

Use the **Force Selected Signal** dialog box to enter parameters to force a VHDL signal, Verilog wire, or a Verilog reg to a constant value. This dialog box opens when you select a signal then right-click the **Force Constant** option. After you assign a new constant force, those values override the assignments made from within HDL code or any previously applied constant or clock force. Click **Apply** to apply all changes. Figure 2-3 shows the Force Selected Signal dialog box.

Figure 2-3: Force Selected Signal Dialog Box

The Force Selected Signal options are:

### Signal Name

Displays the default signal name. The default signal name is the full path name of the selected item. You can change the signal name in the edit box. When you enter an invalid signal name in the edit box, the edit box turns red.

### • Value Radix

Displays the current radix setting of the selected signal. You can choose one of the supported radix types - Binary, Hexadecimal, Unsigned Decimal, Signed Decimal, Octal, and ASCII.

### Force to Value

Specifies a force constant value using the defined radix value.

### • Starting at Time Offset

Starts after the specified time. The default starting time is 0. Time can be a string, such as "10" or "10 ns." When you enter a number without a unit, ISim uses the default.

#### • Cancel after Time Offset

Cancels after the specified time. Time can be a string such as 10 or 10 ns. When a number entered without a unit, the default simulation time unit is used.

### Applying Clock Stimulus

When you right-click **Force Clock**, you can use the **Define Clock** dialog box to enter parameters to force a VHDL signal, Verilog wire, or a Verilog reg to an alternating pattern (clock). The newly applied clock pattern overrides assignments made from within HDL code or any previously applied constant or clock force. Click **Apply** to apply changes.

### **Define Clock Dialog Box**

Right-click **Force Clock** to open the **Define Clock** dialog box. The options in the dialog box are:

#### Signal Name

Displays the default signal name, which is the full path name of the item selected in the Objects panel or waveform. You can change the signal name in the edit box. When you enter an invalid signal name in the edit box, the edit box turns red.

Note: Running the restart command cancels all the effective isim force commands.

#### • Value Radix

Displays the current radix setting of the selected signal. You can choose one of the supported radix types from the dropdown box: Binary, Hexadecimal, Unsigned Decimal, Signed Decimal, Octal, and ASCII.

### Leading Edge Value

Specify the first edge of the clock pattern. The Leading Edge Value uses the radix defined in Value Radix.

### • Trailing Edge Value

Specify the second edge of the clock pattern. The Trailing Edge Value uses the radix defined in the **Value Radix** field.

### Starting at Time Offset

Start the force command after the specified time from the current simulation. The default starting time is 0. Time can be a string, such as 10 or 10 ns. If you enter a number without a unit, ISim uses the default user unit as returned by the isim get userunit Tcl command.

#### Cancel after Time Offset

Cancel the force command after the specified time from the current simulation time. Time can be a string, such as 10 or 10 ns. When you enter a number without a unit, ISim uses the default simulation time unit.

#### Duty Cycle (%)

Specify the percentage of time that the clock pulse is in an active state. The acceptable value ranges from 0 to 100.

#### Period

Specify the length of the clock pulse, defined as a time value. Time can be a string, such as 10 or 10 ns.

### **Define Clock Settings Examples**

To assign a permanent clock to a signal (100 MHz clock), set the following fields:

- Leading Edge Value: 1

- Trailing Edge Value: 0

- Starting at Time Offset: 0

- Cancel after Time Offset: <blank>

- **Duty Cycle (%):** 50

- Period: 10 ns

To assign a clock to a signal for a specific period of time (start toggling at 100 ns, stop toggling after 1 ms), set the following fields:

- Leading Edge Value: 1

- Trailing Edge Value: 0

- Starting at Time Offset: 100 ns

- Cancel after Time Offset: 1 ms

- **Duty Cycle (%):** 50

- Period: <specify clock period>

To assign a toggling value for a signal (toggle between hex F and hex A every 50 ns for 1us), set the following fields:

- Value Radix: Hexadecimal

- Leading Edge Value: F

- Trailing Edge Value: A

- Starting at Time Offset: 0

- Cancel After Time Offset: 1us

- **Duty Cycle (%)**: 50

- Period: 50 ns

### **Setting ISim Preferences**

The preference settings let you view and change the settings for ISim. To set preferences:

- 1. Select **Edit > Preferences**.

- 2. In the left pane of the Preferences dialog box, click a category to view.

- ISE Text Editor Preferences

- ISim Simulator Preferences

- 3. Make the necessary setting changes.

- 4. Click the **Apply** button, and then click **OK**.

The Preference settings are saved and are effective immediately in your ISim session.

### ISE Text Editor Preferences

The preference setting associated with ISE Text Editor controls the behavior of Hardware Description Language (HDL) files open in ISim only. For more information about the preference settings, see the <u>ISE Text Editor</u> Help.

### **ISim Simulator Preferences**

Use the ISim Simulator page in the **Preferences** dialog box. Select **Edit > Preferences > ISim Simulator** in the left pane.

#### **Draw Waveform Shadow**

Shows or hides the shadow background for signals in the Wave window.

### Limit the maximum number of elements display to

Sets limit for number of children elements to display for objects in the Object window. See Showing Display Elements.

#### **Default Radix**

Sets the default radix value displayed in the wave configuration, the Objects panel, and the Console panel. See Changing the Default Radix.

#### Console text font

The window to the right of the field shows example text for the specified font. Click the **Change** button to open a dialog box in which you can specify the font used in the Console.

### **ISim Color Preferences**

Use the Colors page to set your color preferences for displaying the waveform. Click **Apply** to apply changes. The color preference options are:

#### Current Color Scheme

Displays the default color scheme and any custom schemes you have created.

#### New

Creates a new scheme. Enter the new name in the **Current Color Scheme** field and edit the colors in the scheme table.

#### Delete

Deletes the custom scheme that you have selected. You can edit the color of this scheme.

See Setting ISim Preferences, page 32.

### Time Format Preferences

You can customize the appearance of displayed time values using the **Time Format Preferences**. Select **Edit > Preferences > Time Format** in the left pane. The following subsections describe the two categories of time formats.

#### Waveform Window

Time format options apply to the GUI elements inside the waveform viewer window. The time format options are:

#### Link All Waveform Time Units To Ruler

Is on by default and keeps the Units setting of the Cursors/Markers and Measure Bubble categories in sync with changes to the Ruler category.

#### Rulers

Applies to the main ruler at the top of the waveform window as well as to the floating ruler.

#### • Cursors/Markers

Applies to the time values displayed for the all cursors and markers.

#### • Measure Bubbles

Applies to the cursor value bubbles displayed at the bottom of the waveform window.

### Other GUI Elements

The time format options apply to the GUI elements outside the Waveform window as follows:

#### All Time Values

Applies to the current simulation time shown at the bottom right of the main window and time values shown in the Objects panel. Time formats allow setting of time units and precision of display of values using following fields:

### • Units

Lets you set the units for time values. The default settings for the Other GUI elements is **Default**; for the Waveform Window, the default is **Auto**.

#### • Decimal Places

Lets you set the number of decimal places to be used in displaying time values. The default setting for all categories that have a setting is Maximum.

#### • Reset To Defaults

Resets the values to the original default settings.

# Chapter 3

# Compilation and Simulation

You can run simulation for VHDL, Verilog, or Mixed Language components.

- Functional Simulation can be run early in the design process.

- Timing Simulation must be run post-Place and Route (PAR)

In addition to the two types of simulation, you have the options of running simulation as follows:

- From a Tools Command Language (Tcl) batch file or from the command line using Tcl

commands.

- From the GUI, which can be invoked from either the ISE® Design Suite or the PlanAhead™ tools.

Running a simulation from the command line for either a Functional or a Timing simulation requires the following steps:

- 1. Parsing design files

- 2. Generating a simulation executable

- 3. Simulating the design

There are additional requirements for a Timing simulation, which is described in Timing Simulation (Gate-Level Simulation), page 49.

The following subsections describe these steps.

# **Parsing Design Files**

The vhpcomp and vlogcomp commands parse VHDL and Verilog files, respectively.

# vlogcomp Command

The vlogcomp command parses Verilog source files and generates a binary representation of the Verilog files. The binary representation generated by vlogcomp is used by the fuse command to create a simulation executable.

You must specify either a project file or one or more Verilog source files to compile. If neither the project file nor the Verilog file is specified, vlogcomp issues an error. See Project File Syntax, page 43 for information about the project file.

### vlogcomp Command Syntax

To go to the command description click the option link.