## MCM2114 MCM21L14

#### 4096-BIT STATIC RANDOM ACCESS MEMORY

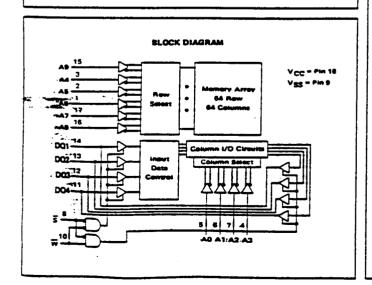

The MCM2114 is a 4096-bit rendom access memory tabricated with high density, high reliability N-chennel silicon-gate technology. For ease of use, the device operates from a single power supply, is directly compatible with TTL and DTL, and requires no clocks or refreshing because of fully static operation. Data access is particularly simple, since address setup times are not required. The output data has the same potenty as the input data.

The MCM2114 is designed for memory applications where simple interfacing is the design objective. The MCM2114 is assembled in 18-pin dual-in-line packages with the industry standard pin-out. A separate chip select (\$\oldsymbol{S}\$) lead allows easy selection of an individual package when the three-state outputs are OR-field.

The MCM2114 sense has a maximum current of 100 mA. Low power versions (i.e., MCM21L14 sense) are available with a maximum current of only 70 mA.

- 1024 Words by 4-Bit Organization -

- Industry Standard 18-Piri Configuration

- Single +5 Volt Supply

- No Clock or Timing Strobe Required

- Fully Static: Cycle Time = Access Time

- Maximum Access Time MCM2114-20/MCM21L14-20 200 ns MCM2114-25/MCM21L14-25 250 ns MCM2114-30/MCM21L14-30 300 ns MCM2114-45/MCM21L14-45 450 ns

- Fully TTL Compatible

- Common Data input and Output

- Three-State Outputs for OR-Ties

- Low Power Version Available

### MOS

(N-CHANNEL, SILICON-GATE)

4096-BIT STATIC RANDOM ACCESS MEMORY

#### PIN ASSIGNMENT

|   | 18                         | PVCC                               |

|---|----------------------------|------------------------------------|

| 2 | 17                         | 3A7                                |

| 3 | 16                         | BAB                                |

| 4 | 15                         | DA9                                |

| 5 | 14                         | 1001                               |

| 6 | 13                         | 1002                               |

| 7 | 12                         | 003                                |

| 8 | 11                         | DO4                                |

| 9 | 10                         | w                                  |

|   | 3<br>4<br>5<br>6<br>7<br>8 | 2 17 3 16 4 15 5 14 6 13 7 12 8 11 |

| PI        | N NAMES           |

|-----------|-------------------|

| AO-A9     | Address input     |

|           | Write Enable      |

| <u> 5</u> | Chip Select       |

| DQ1-DQ4   | Data Input/Output |

| VCC       | Power (+5 V)      |

| VSS       | Ground            |

#### ABSOLUTE MAXIMUM RATINGS (See Note)

| Rating                                 | Vatue       | Unit |

|----------------------------------------|-------------|------|

| Temperature Under Bias                 | -10 to +80  | o.c  |

| Voltage on Any Pin With Respect to VSS | -0.5 to +70 | V    |

| OC Output Current                      | 5.0         | MΑ   |

| Power Dissipation                      | 10          | msW  |

| Operating Temperature Range            | 0 to +70    | •€   |

| Storage Temperature Range              | -65 to +150 | °C   |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERAT-ING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliabilisty. This device contains circuitry to protect the inputs against damage due to high static voltages or electric helds; however, it is advised that normal precausions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.

## DC OPERATING CONDITIONS AND CHARACTERISTICS (Full operating voltage and temperature range unless otherwise noted.)

#### RECOMMENDED OC OPERATING CONDITIONS

| Parameter                   | Symbol | Min  | Typ | Max  | Unit |

|-----------------------------|--------|------|-----|------|------|

| Supply Voltage              | VCC    | 4 75 | 5.0 | 5.25 |      |

|                             | VSS    | 3    | Ü   | 3    | 1 '  |

| Logic 1 Voltage, All Inputs | VIH    | 2.0  | -   | 60   | V    |

| Logic 0 Voltage, All Inputs | VII    | -0.5 | -   | 0.8  | V    |

#### DC CHARACTERISTICS

| Personeur                                                       | S               | MCM2114 |     |     | MCM21L14 |     |     | ļ., . |

|-----------------------------------------------------------------|-----------------|---------|-----|-----|----------|-----|-----|-------|

|                                                                 | Symbol          | Min     | Typ | Max | Min      | Typ | Max | Unit  |

| inout Load Current (All Inout Pins, V <sub>m</sub> =0 to 5.5 V) | (t <sub>e</sub> | -       | -   | 10  |          | -   | 10  | AM.   |

| 1/O Leakage Current (S = 2.4 V. VDQ = 0.4 V to VCC)             | iltoi           | -       | -   | 10  | _        | -   | 10  | FA.   |

| Power Supply Current (V-n=5.5 V, 10Q=0 mA, T4 = 25°Cl           | Icci            | -       | 30  | 95  | _        | -   | 65  | mA    |

| Power Supply Current (Vin = 5.5 V, IDQ = 0 mA, IA = 0°Cl        | Ices            | ~       | -   | 100 | -        | -   | 70  | mA    |

| Output Low Current VOL = 0 4 V                                  | 'OL             | 21      | 60  | -   | 2.1      | 6.0 | -   | mA    |

| Output High Current VOH # 2.4 V                                 | IOH             |         | -14 | -10 | -        | -14 | -10 | mA    |

NOTE: Duration not to exceed 30 seconds.

### CAPACITANCE (I = 1.0 MHz, TA = 25°C, periodically sampled rather than 100% rested!

| Charactanetic                      | Symbol | Max | Unit |

|------------------------------------|--------|-----|------|

| Inout Capacitance (Vin = 0 V)      | C.n    | 5.0 | ρF   |

| Input/Output Capacitance (VDQ=0 VI | Ci/O   | 5.0 | of   |

Capacitance measured with a Boonton Meter or effective capacitance calculated from the equation:  $C = i \frac{\partial x}{\partial x} \Delta y$ .

# AC OPERATING CONDITIONS AND CHARACTERISTICS (Full operating voltage and temperature unless otherwise noted.)

| Input Pulse Levels        | Input and Output Timing Levels         |

|---------------------------|----------------------------------------|

| Input Rise and Fall Times | Output Load 1 TTL Gate and Ct = 100 pf |

#### READ (NOTE 1), WRITE (NOTE 2) CYCLES

| Pärameter                            | Symbol | MCM2114-20   MCM21L14-20 |     | MCM2114-25<br>MCM21L14-25 |      | MCM2114-30<br>MCM21L14-30 |     | MCM2114-45<br>MCM21L14-45 |     | Unit |

|--------------------------------------|--------|--------------------------|-----|---------------------------|------|---------------------------|-----|---------------------------|-----|------|

|                                      |        | Min                      | Max | Min                       | Mass | Min                       | Mex | Min                       | Max | Ĭ    |

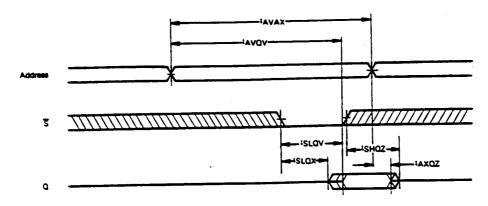

| Address Valid to Address Don't Care  | TAVAX  | 300                      |     | 250                       | _    | 300                       | -   | 450                       | -   | ns   |

| Address Valid to Output Valid        | VDVA?  | -                        | 200 | -                         | 250  | -                         | 300 | -                         | 450 | ns   |

| Chip Select Low to Data Valid        | ISLQV  | -                        | 70  | _                         | 85   | -                         | 100 | -                         | 120 | ns.  |

| Chip Select Low to Output Don't Care | ISLOX  | 20                       | -   | 20                        | -    | 20                        | -   | 20                        | -   | ns   |

| Chip Select High to Output High Z    | ISHQZ  | -                        | 60  | -                         | 70   | -                         | 90  | -                         | 100 | ns   |

| Address Don't Care to Output High Z  | IAXOZ  | <del>5</del> 0           | _   | 50                        | -    | 50                        | -   | 50                        |     | ns   |

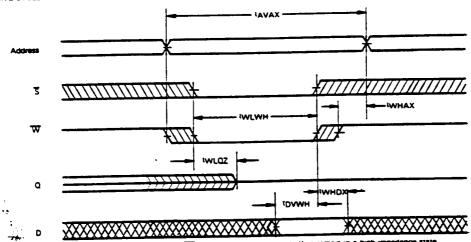

| Write Low to Write High              | IWLWH  | 120                      | -   | 135                       | -    | 150                       | -   | 500                       | -   | ns.  |

| Witte High to Address Don't Care     | XAHW   | J                        | -   | 0                         | +    | 0                         | -   | 0                         | _   | ns   |

| Write Low to Output High Z           | IWLOZ  | _                        | 60  | -                         | 70   | _                         | 90  | _                         | 100 | ns   |

| Data Valid to Winte High             | IDVWH  | 120                      | -   | 135                       | -    | 150                       | -   | 300                       | -   | ns.  |

| Write High to Data Con't             | (WHOX  | J                        | -   | 0                         | -    | 0                         | -   | 0                         | -   | ns   |

NOTES: 1 A Reed occurs during the overlap of a low 5 and a mon W

<sup>2.</sup> A Write occurs during the overlap of a low S and a low W.

### READ CYCLE TIMING (W HELD HIGH)

## WRITE CYCLE TIMING (NOTE 3)

If the S low transition occurs simultaneously with the W low transition, the output buffers remain in a right-imposition state.

| <u> </u> |                    | WAVEFORM                               | \$                           |

|----------|--------------------|----------------------------------------|------------------------------|

|          | Wassierm<br>Symbol | Imput                                  | Quesus                       |

|          |                    | MUST BE<br>VALID                       | WHLL BE                      |

|          | IIII               | CHANGE<br>FROM H TO L                  | WILL CHANGE<br>FROM H TO L   |

|          |                    | CHANGE<br>FROM L TO H                  | WILL CHANGS                  |

| 1        | <b>****</b>        | DON'T CARE.<br>ANY CHANGE<br>PERMITTED | CHANGING<br>STATE<br>UNEMDIM |

| <u></u>  | $\Rightarrow$      | -                                      | HIGH                         |